## ASU-MIPEX Graduation Project 2013 High Speed Serial Links Supervised by: Dr. Sameh Assem Ibrahim

## **High Speed Serial Links**

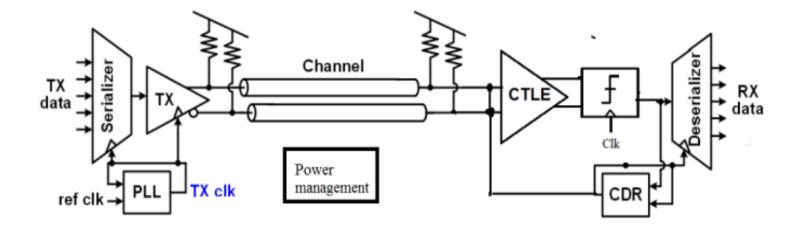

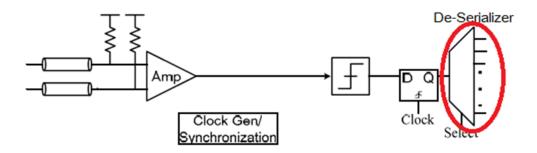

System Block Diagram

### Outlines

- Bias Cell

- LDO

- Transmitter

- Receiver

- PLL

# Bias Cell

Presented by : Salma El-Sawy

### Outlines

- Bias Cell

- Band gap Reference circuit1

- Band gap Reference circuit2

- Comparison and Decision

- Startup circuit

- Folded Cascode OTA

- Biasing Folded Cascode

- Corners

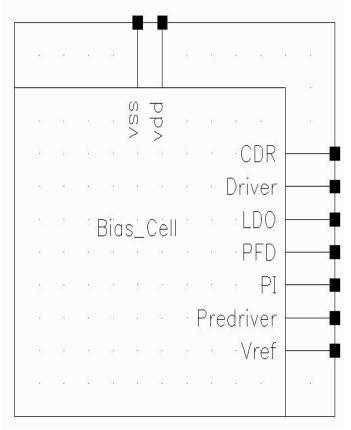

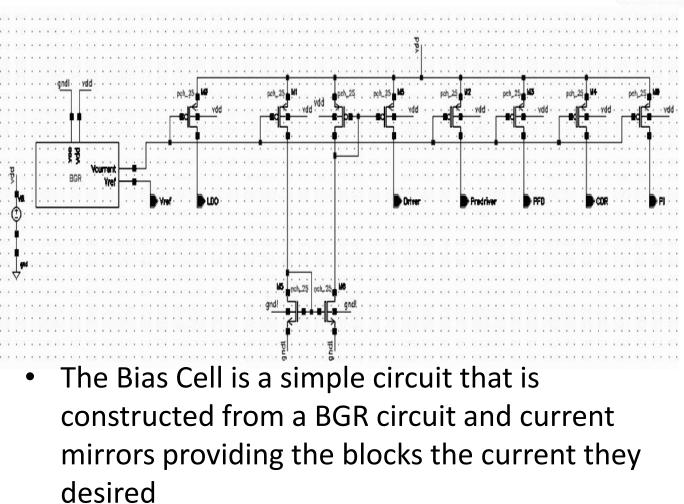

## **Bias Cell**

- The bias Cell is an important block, to provide the system block the desired Currents

- It is also necessary for providing a Constant reference voltage with the variations of the Supply and temperature

## **Bias Cell**

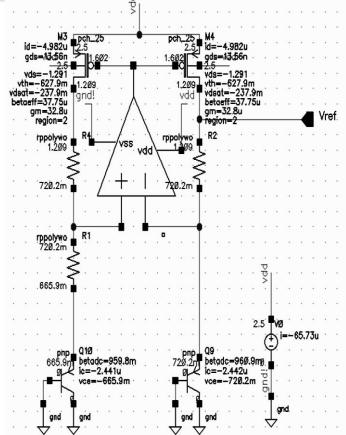

#### BGR with PTAT curren\*

- This band Gap Circuit Provide Constant Vref across PVT

- And Provide a PTAT current that increases with the Temperature

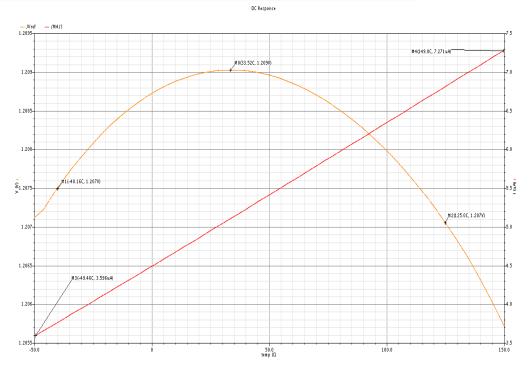

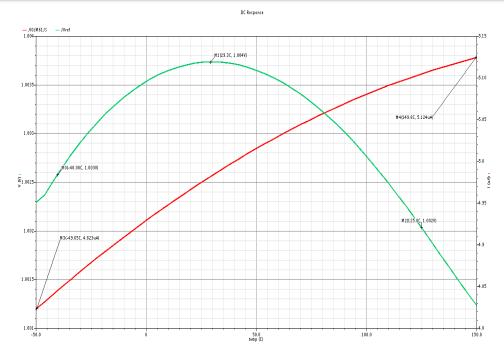

- This shows Vref and Iref Vs. Temperature

- Where the Voltage varies 2mV in the temperature interval [-40,125]

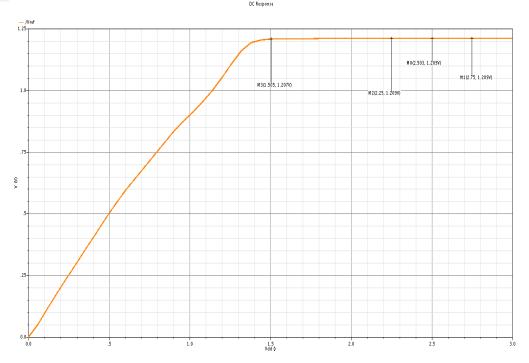

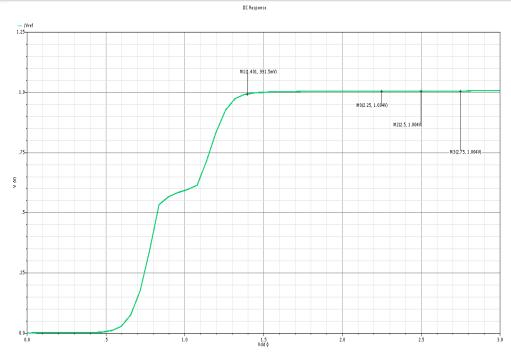

- This shows Vref Vs. supply variations

- Which shows that Vref is almost unchanged for 10% variation of the supply, also the circuit will function properly till 1.5v supply

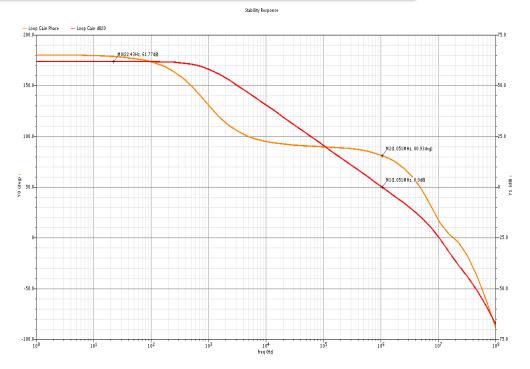

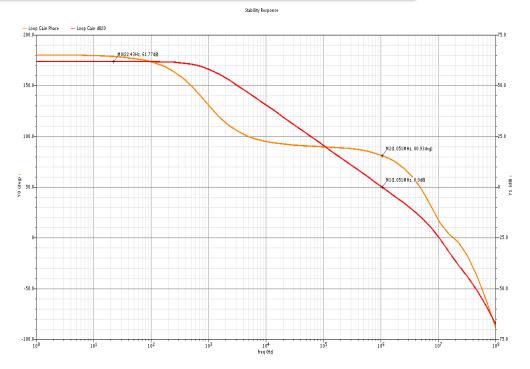

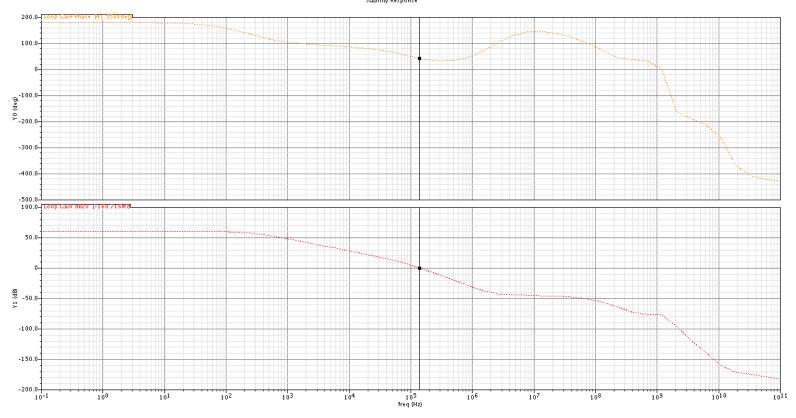

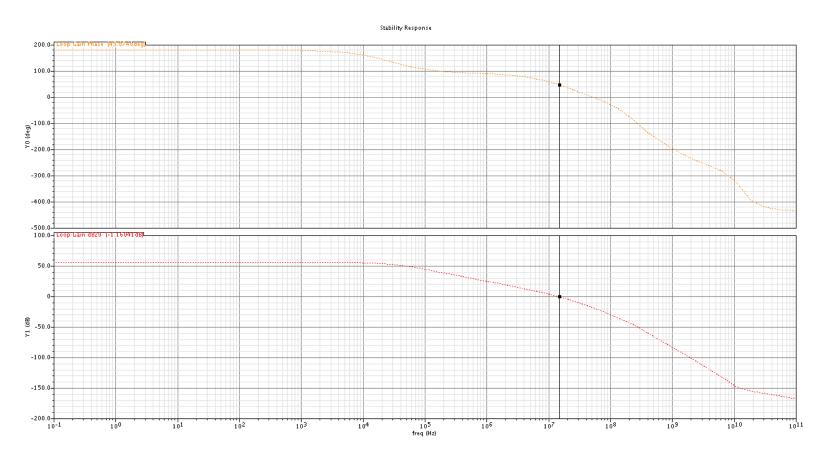

- This shows the stability analysis of our BGR

- Where the PM=80.93 degree

#### **BGR with PTAT current Outputs :-**

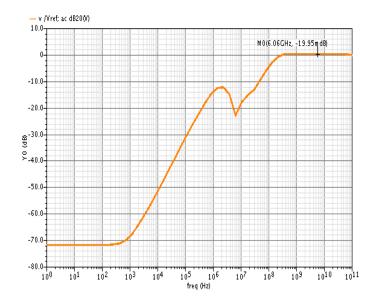

The PSR is as shown in figure =19.95m dB

• Which isn't a good rejection ratio

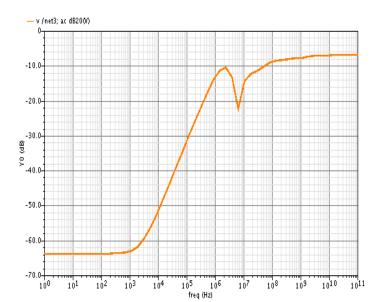

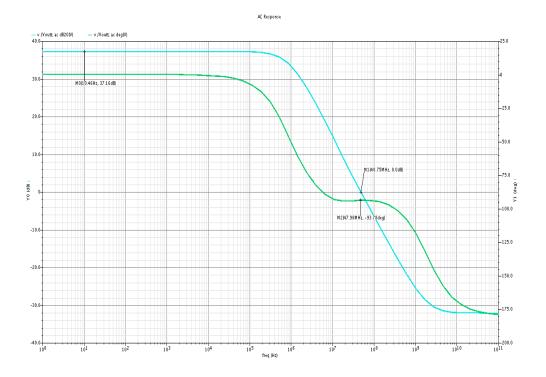

AC Response

- This shows the stability analysis of our BGR

- Where the PM=80.93 degree

#### **CMOS BGR with Sub-1-V operation.**

- This BGR Provide us Both Constant Voltage and Constant Current references

BUT, PRACTICALLY due to that our resistors are on chip non ideal resistors having a Temperature

- You can get either Constant current OR Constant Voltage by adjusting the Resistors ratios

- This shows Vref and Iref Vs. Temperature

- Where the Voltage varies 2mV in the temperature interval

#References

-40,125

7/10/2013

#### **CMOS BGR with Sub-1-V operation "Outputs".**

- This shows Vref Vs. supply variations

- Which shows that Vref is almost unchanged for 10% variation of the supply, also the circuit will function properly till 1.4v supply

#### CMOS BGR with Sub-1-V operation "Outputs".

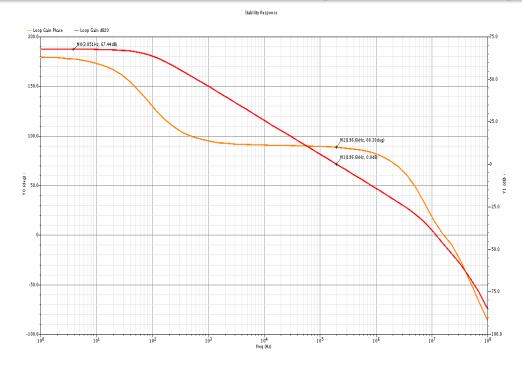

- This shows the stability analysis of our BGR

- Where the PM=88.38 degree

AC Response

- The PSR is as shown in figure =-7 dB

- Which is a better Ratio.

### **Comparison and Decision**

| Points of<br>Comparison | <b>BGR with PTAT Current Output</b>                        | BGR with Sub 1-V oper                                                                                                                                                       |  |  |

|-------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| VREF                    | Can't be controlled always =1.206v<br>Varies with temp 2mV | Designed to be 1V "adj<br>Varies with temp 2                                                                                                                                |  |  |

| IREF                    | PTAT current Increase with<br>Temperature                  | Constant current , BU<br>due to no ideal Resi                                                                                                                               |  |  |

| Stability               | Good stability<br>Depending on the design of the OTA       |                                                                                                                                                                             |  |  |

| PSR                     | Bad                                                        | Good                                                                                                                                                                        |  |  |

| TC                      | 10.034 * 10 <sup>-6</sup> ppm/c                            | 12.0849 * 10 <sup>-6</sup> pp                                                                                                                                               |  |  |

|                         | Comparison<br>VREF<br>IREF<br>Stability<br>PSR             | ComparisonVREFCan't be controlled always =1.206v<br>Varies with temp 2mVIREFPTAT current Increase with<br>TemperatureStabilityGood state<br>Depending on the defendedPSRBad |  |  |

#### That is Why I Decide to Use the BGR with 1-V operation

#References

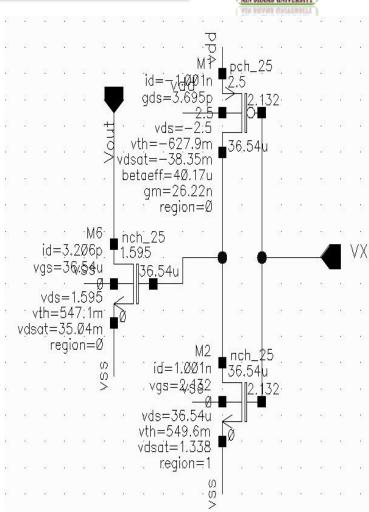

## **Startup Circuit**

- This startup Circuit is an important part of the BGR circuit

- Where the BGR have a parasitic operating point when the Current is equal to zero

- In order to move from this point to the desired operating point we inject a current in the band Gap at its startup.

- Then the Startup Circuit is Designed to be switched off when the BGR reach its steady State.

## **Startup Circuit**

AIN SHAMS UNIVERSITY

- This startup circuit consist of an inverter and an NMOS.

- Initially I=0, then Vx=0 so the output of the inverter is Vdd

- so M6 is ON passing current in the BGR so Vx start to increase till the output of the inverter is Low M6 is OFF, when we reached the steady state.

ASU-MIPEX Graduation Project 2013

Transient Response

— Vout — Vdd - Vout inverter 3.0-MO(7.274us, 2.5V) Vdd 2.5-M1(7.079us, 2.133V) ٧x 2.0 M2(7.071us, 1.595V) Vout\_startup 1.5χ 1.0 Vout\_inverter 2.0 4.0 8.0 6.0 time (us)

7/10/2013

#References

ASU-MIPEX Graduation Project 2013

22

- OTA is used as a Feedback Element To adjust the 2 point VA and VB for the functionality of the BGR.

- Also it is used for biasing the BGR PMOS with its desired input

- In this part of the presentation I will be discussing Different Topologies of OTA and why Did I made that Choice.

#### **NMOS single ended Simple OTA:-**

- In order to Get the Desired VCM.

- We found that the Transistors Vod is <100m</li>

- Which leads to increasing the probability for the mosfet to enter the Sub threshold.

#References

#### **NMOS single ended Simple OTA:-**

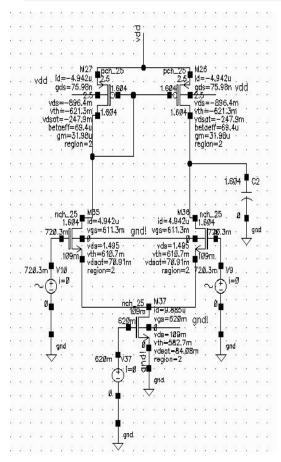

• OTA Stability and Gain . Where the gain is 52dB and the PM is 69.8degree.

#References

#### PMOS single ended Simple OTA:-

- Finding that the input CM is so small so I used PMOS Simple OTA

- We found that the Transistors Vod is <100m</li>

- Which leads to increasing the probability for the mosfet to enter the Sub threshold.

- And also couldn't achieve the desired Output VCM.

#### **PMOS single ended Simple OTA:-**

• OTA Stability and Gain . Where the gain is 37dB and the PM is 86.25degree.

#### **NMOS single ended Telescopic OTA:-**

- In order to Get the Desired VCM.

- We found that the Transistors Vod is

<100m</li>

- Which leads to increasing the probability for the mosfet to enter the Sub threshold.

#References

#### **NMOS single ended Telescopic OTA:-**

• OTA Stability and Gain . Where the gain is 78dB and the PM is 37.4 degree.

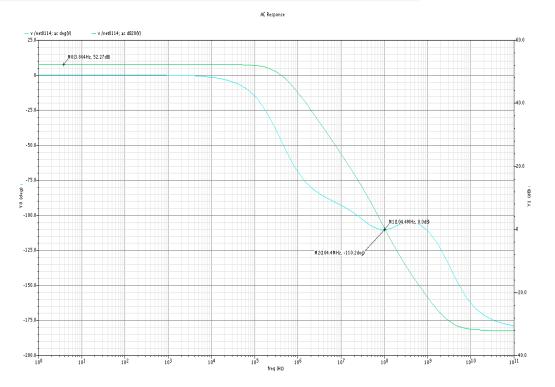

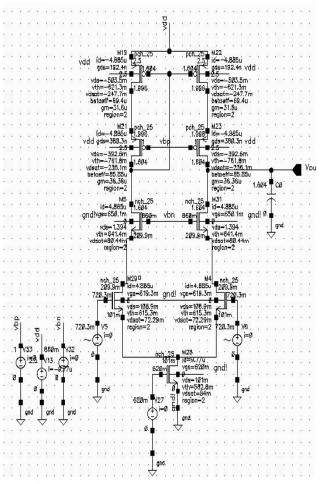

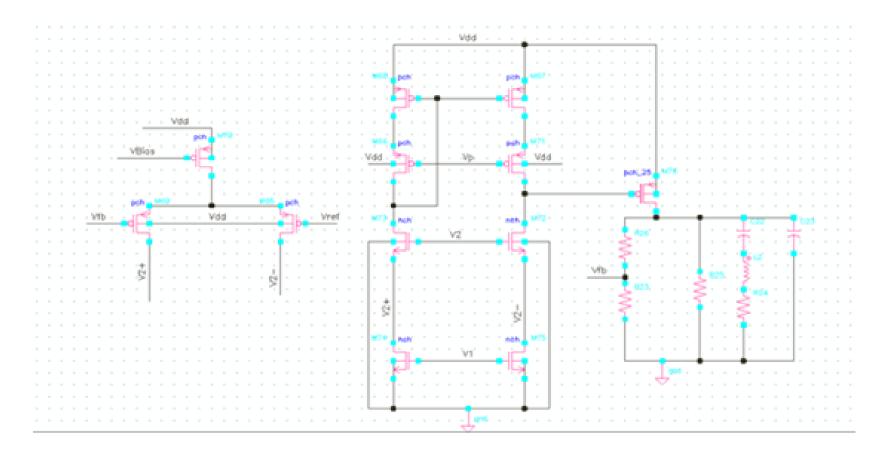

#### **PMOS single ended Folded Cascode OTA:-**

- Since my input is small I used PMOS input

- Getting the desired VCM output

- All transistors Vod>100m decreasing Prob. Of entering region 3

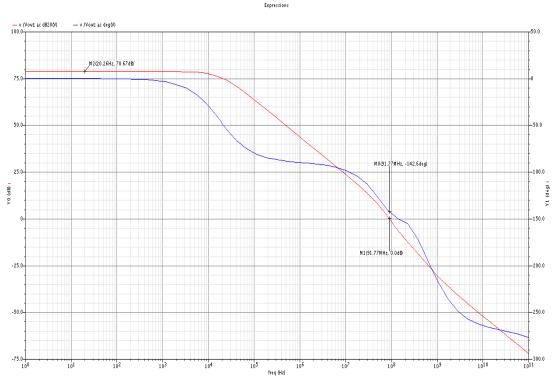

#### **PMOS single ended Folded Cascode OTA:-**

Expression

• OTA Stability and Gain . Where the gain is 70.5dB and the 68 PM is degree.

#References

## **Comparison and Decision**

| Points of<br>Comparison | NMOS i/P<br>Simple OTA          | PMOS i/P<br>Simple OTA             | NMOS i/P<br>Telescopic          | PMOS i/P<br>Folded<br>cascode      |

|-------------------------|---------------------------------|------------------------------------|---------------------------------|------------------------------------|

| Gain                    | Small                           | Small                              | Large                           | Large                              |

| Stability               | Uncondition<br>ally             | Stable                             | Conditionall<br>Y               | Stable                             |

| Vod                     | <100mV                          | <100mV                             | <100mV                          | >100mv                             |

| Input Voltage           | Vi= Vodss<br>+Vod1+Vth<br>Large | Vi=Vdd-Vodss-<br>Vod1-Vth<br>Small | Vi= Vodss<br>+Vod1+Vth<br>Large | Vi=Vdd-Vodss-<br>Vod1-Vth<br>Small |

I chose the Folded Cascode to give me a reasonable gain, desired Output Common mode and chose it to be PMOS input for My Small input Common Mode.

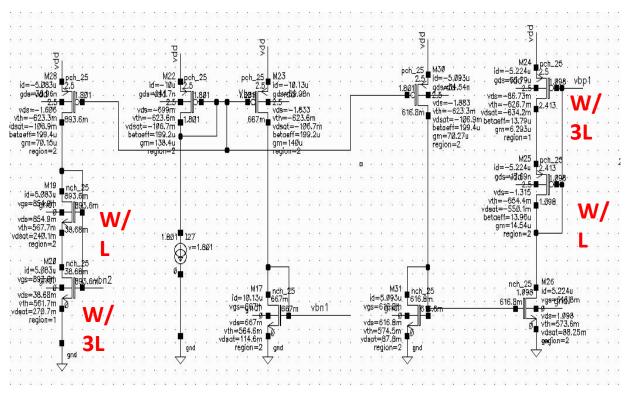

Used To bias the Folded Cascoded OTA Circuit

• Using an Ocean Code to run all Possible corners to get that the Stability is almost the same across corners

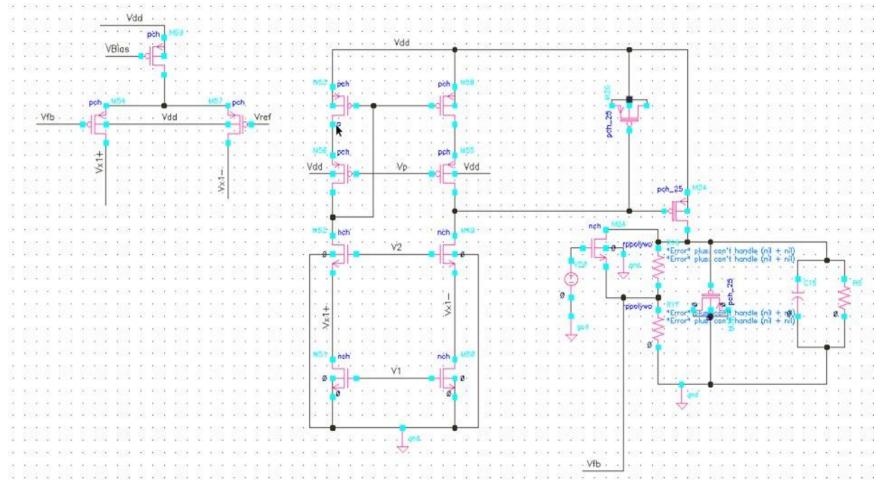

# LDO

#### Presented by : Sherif El-Hosainy

### Outlines

- LDO introduction

- External Cap LDO

- Cap Less LDO

- Final Circuit

- Conclusion

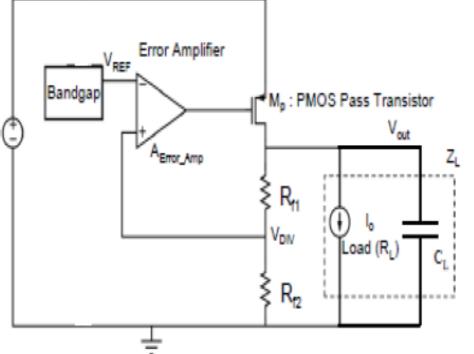

# **LDO introduction**

- LDO Block Diagram

- Stability

- Two Topologies of L

- 1. External Cap LDO

- 2. Cap Less LDO

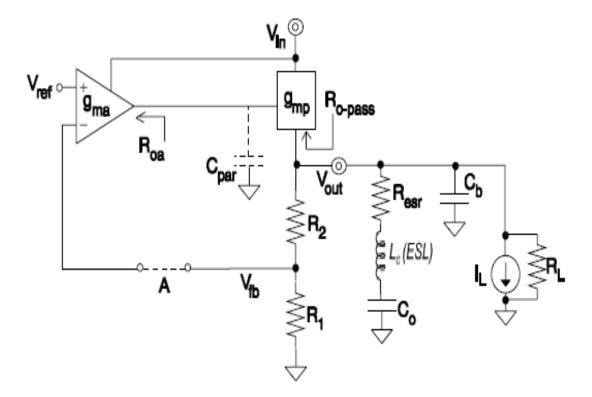

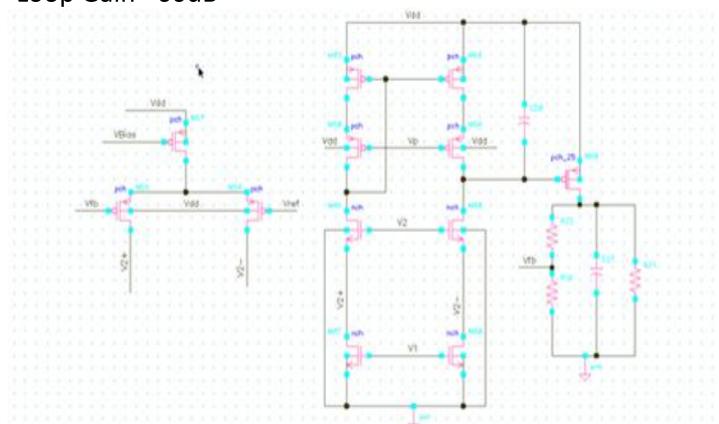

### **External Cap LDO**

• Model for External Cap LDO

• Circuit Schematic

- Total gnd current =67u Integrated Cap

=5p

- Efficiency = 38.7% Loop Gain=60dB

- Non integrated cap model as:

C=4uF Resr=32m ohm

Lesl=1.5nH

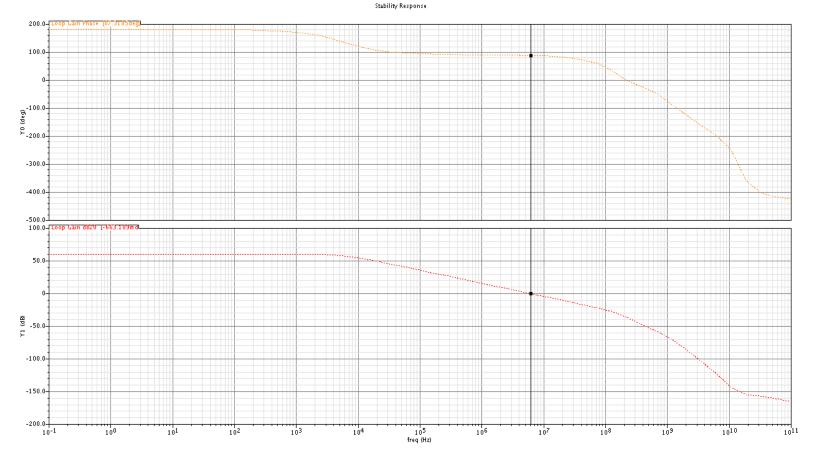

- Circuit Stability analyses under load condition

- Loop Phase =41 degree at OdB

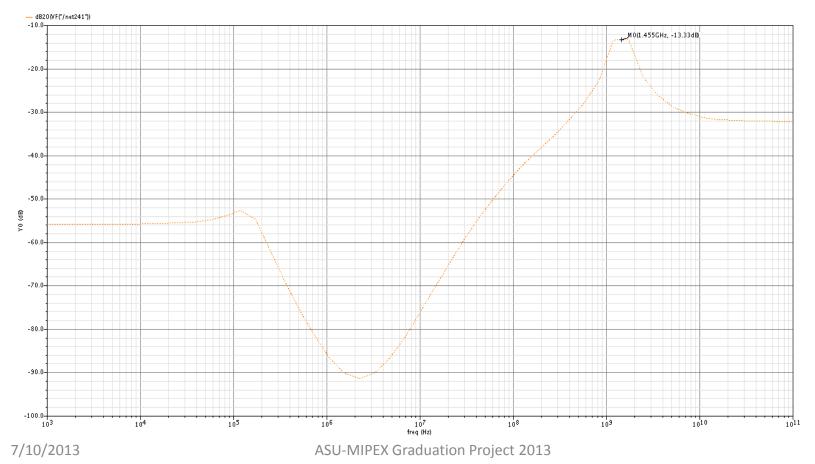

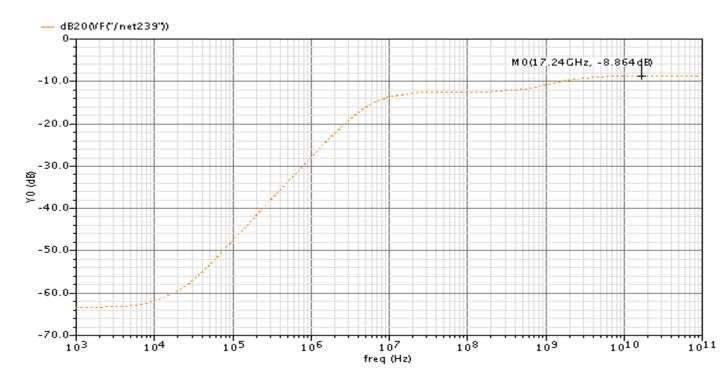

- Circuit PSRR

- Worst case PSRR=-13.33dB

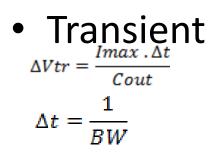

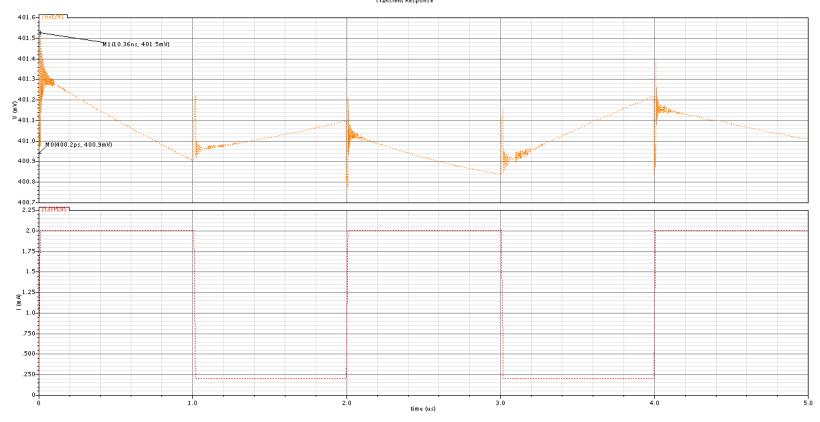

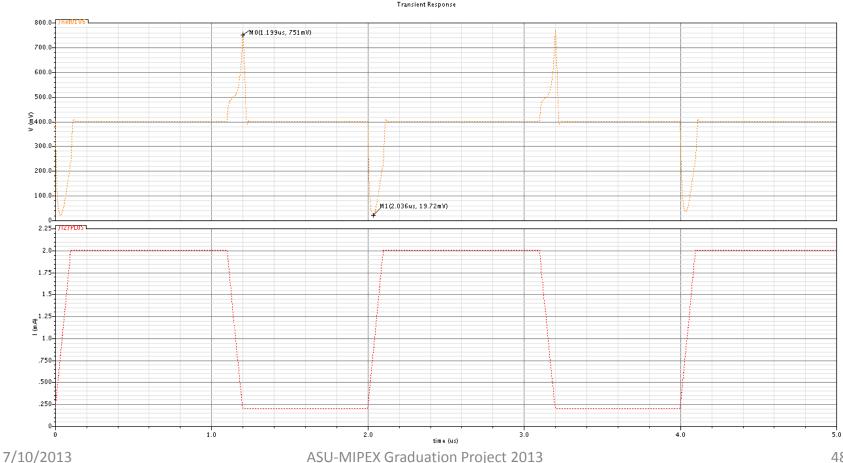

Transient simulation for I load=200u to I load\_max=2m with 1u raise and fall time with Over shot =1.5mV

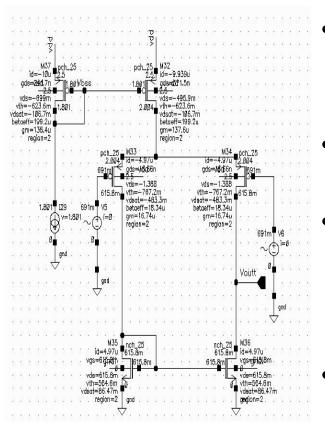

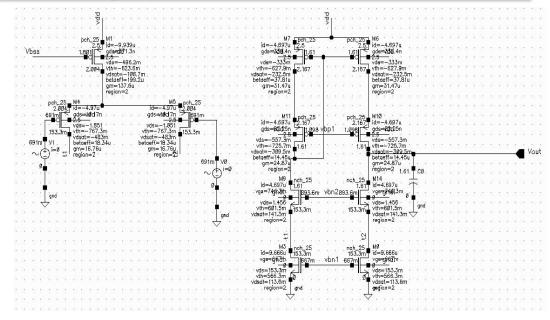

### Cap Less LDO

- Circuit Schematic

- Total gnd current = 85u

- Loop Gain =60dB

Integrated Cap = 8 pF Efficiency=38.3%

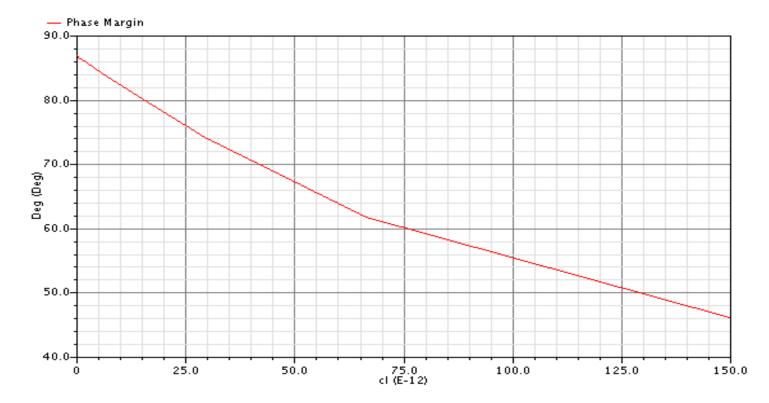

- Circuit Stability analyses under load condition 2mA

- PM=87 degree

- Circuit Stability analyses under no load condition

- PM=45 degree

- Circuit PSRR

- Worst case PSRR= -8.86dB

AC Response

Transient simulation for I load=200u to I load\_max=2m with 1u • raise and fall time with Over and Under shot=350m

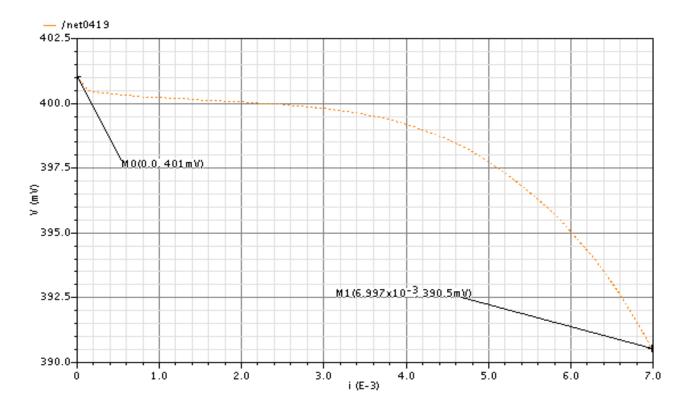

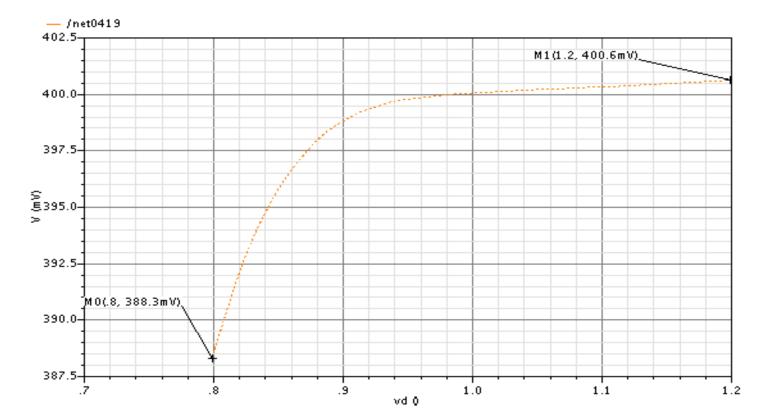

Load Regulation

DC Response

#### • Line Regulation

DC Response

• PM vs CLoad

Expressions

### **Final Circuit**

#### • Cap less LDO with programmable Output

### Conclusion

• External Cap gives Better results in all the parameters.

• Cap Less LDO would be sufficient for stable loads and give fair PSRR.

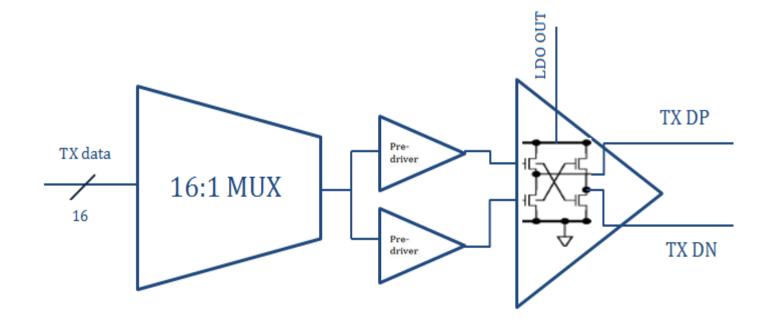

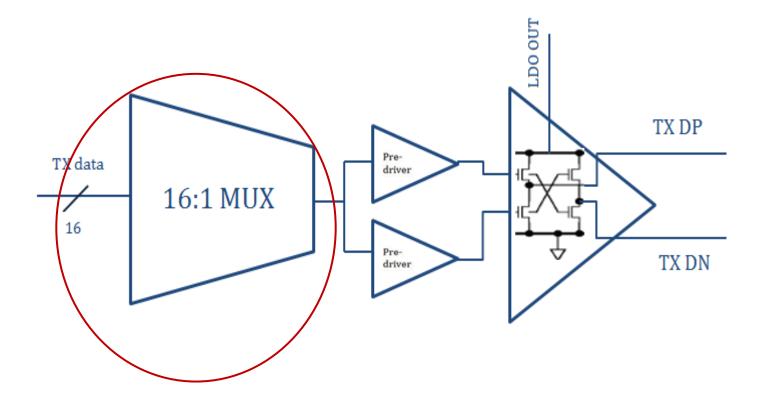

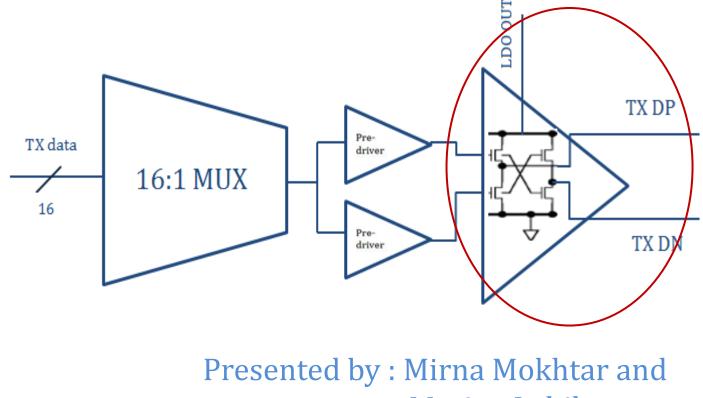

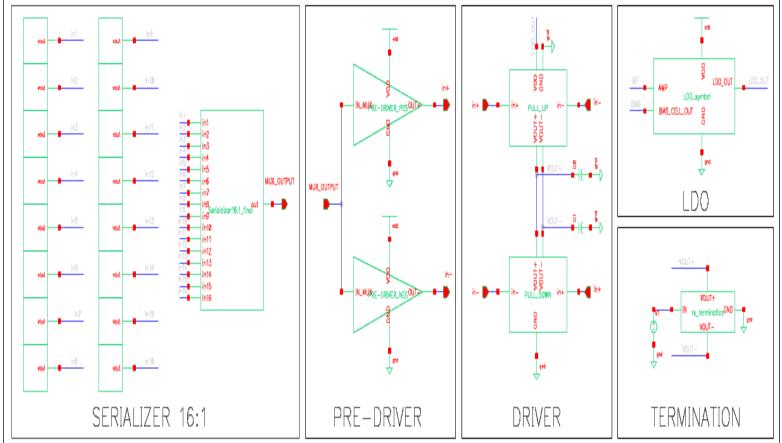

### **Transmitter**

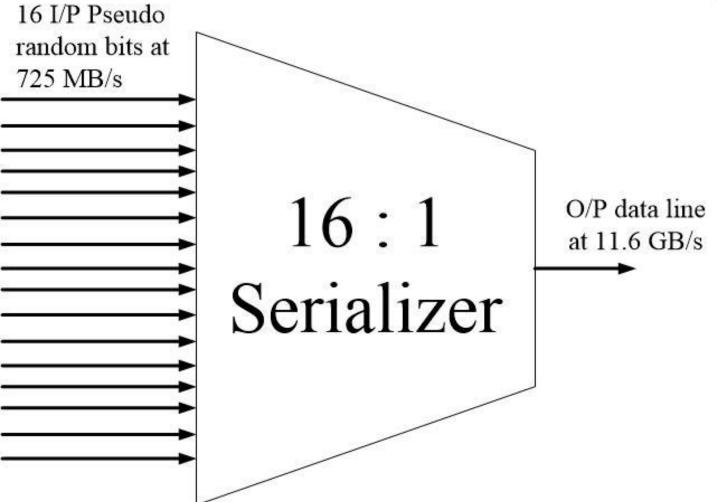

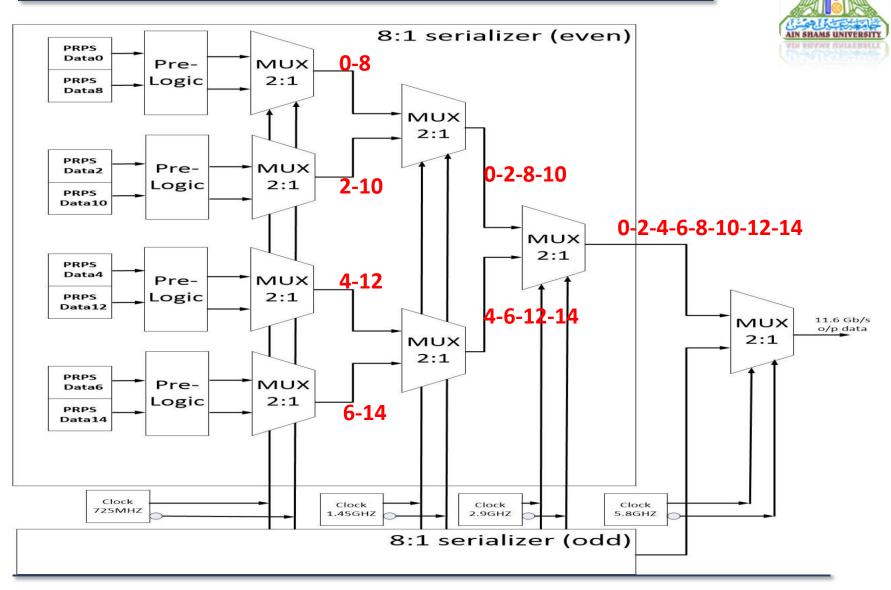

## **16:1 Serialializer**

#### Presented by : Mohamed M.Shafey

- Introduction

- Architecture

- Topology

- Design and Schematic

- Simulation Results

- Layout

### Introduction

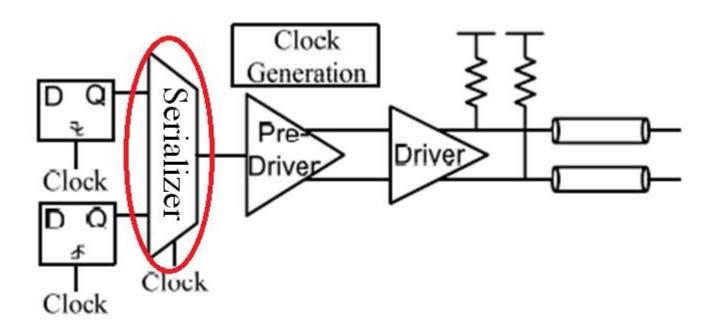

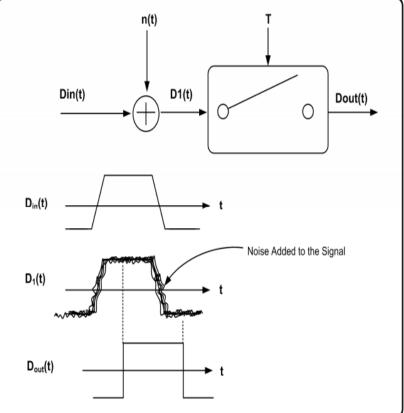

Serializer is serializing parallel input data to a serial output data line.

### Architecture

7/7/2013

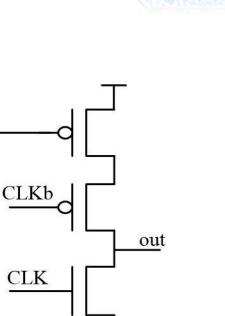

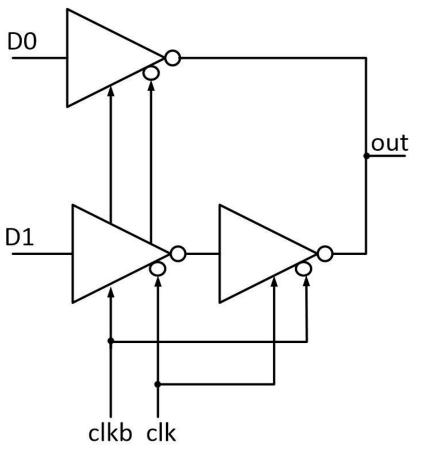

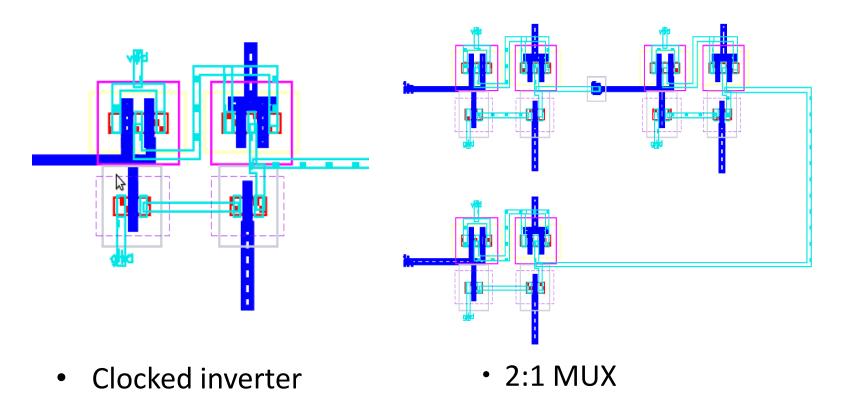

### Clocked Inverter ( $C^2 MOS$ ):

IN

- Inverter that control it's output by a clock

- If CLK = 1 , Inverter pass the input to output

- If CLK = 0 , It holds the data as a latch (<u>high impedance</u>)

- Clocked inverter is a latch

Topology

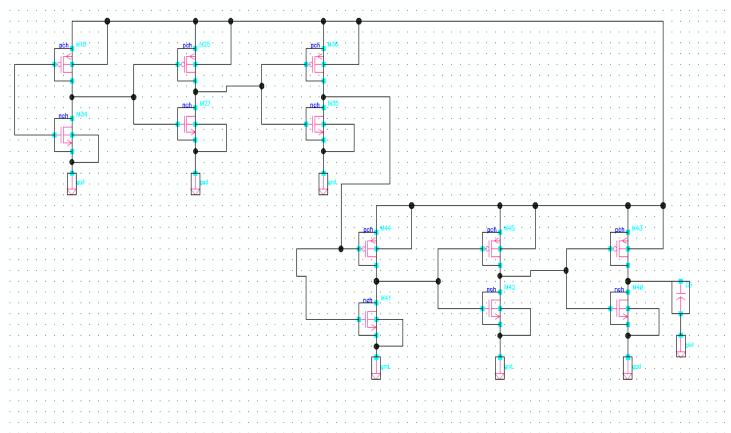

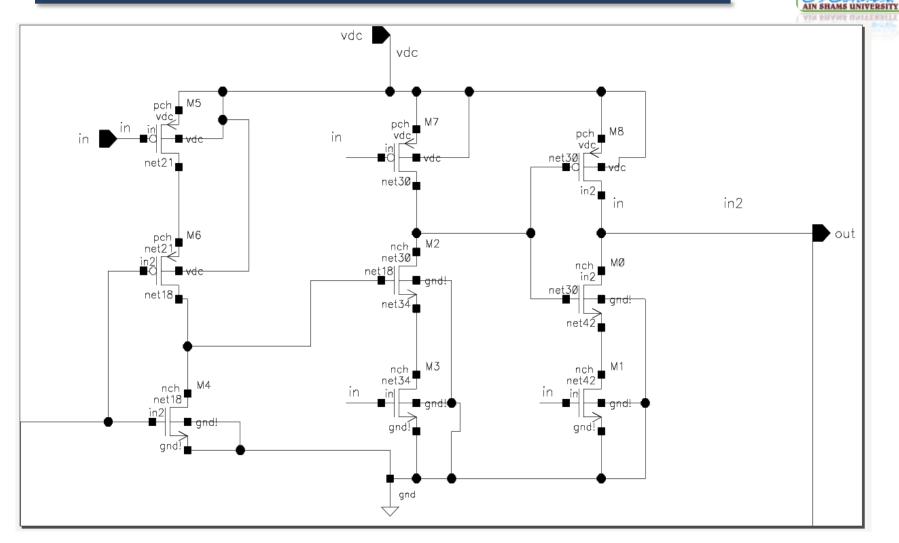

# **Design and Schematic**

- 2:1 multiplexer

- Using 3 clocked inverters we can perform the operation of retiming and selection at the same time

- less power consumption <sup>(C)</sup>

- Decrease Switching components <sup>(C)</sup>

- Node Floating ☺

#### 7/7/2013

#### 61

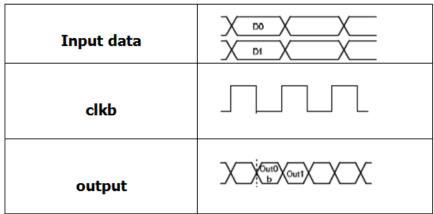

## **Design and Schematic (Cont.)**

- Solving high impedance node (floating )

- Inter state latch

- To hold input level of 2<sup>nd</sup> inverter

## **Design and Schematic (Cont.)**

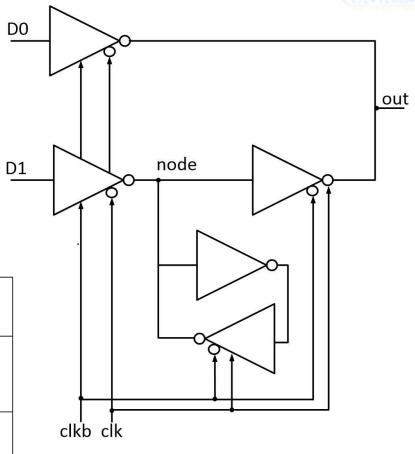

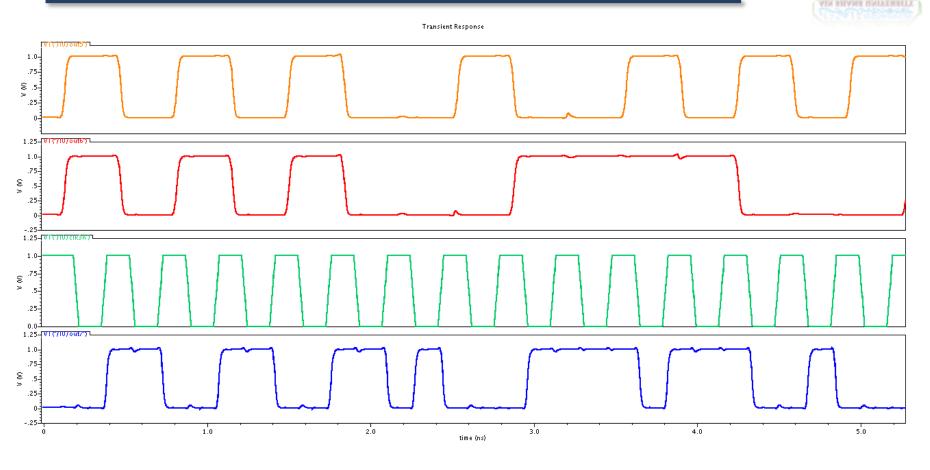

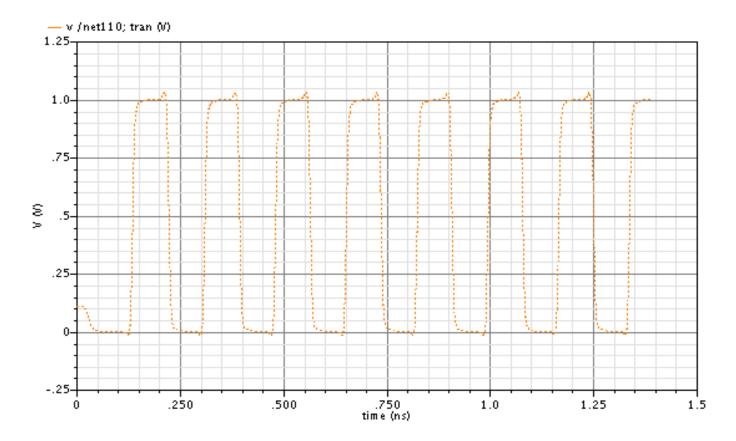

## **Simulation Results**

2 I/P data , CLKb , multiplexed O/P

IN SHAMS UNIVER

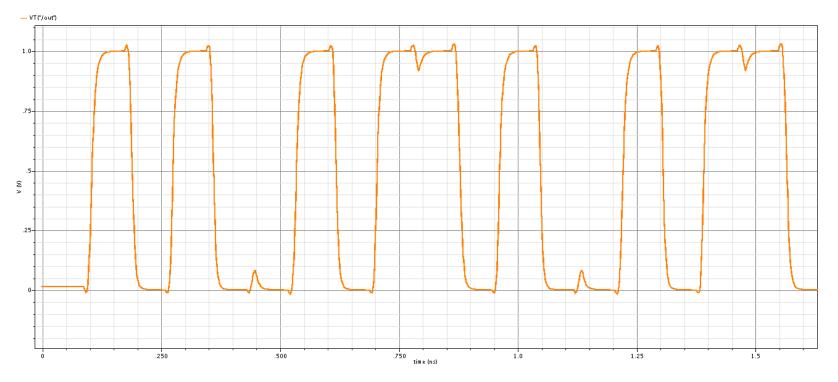

## **Simulation Results (cont.)**

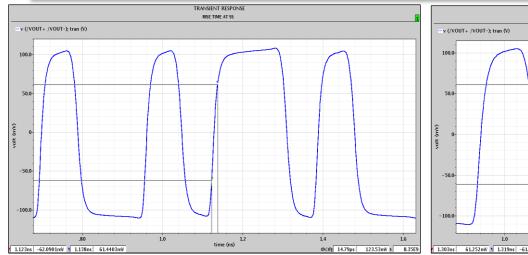

Transient Response

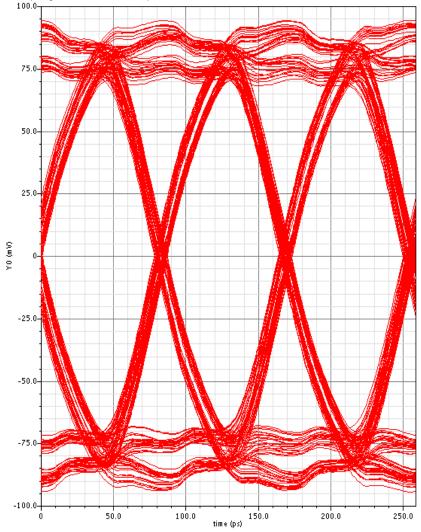

Final Output waveform 11.6 GB/s

## **Simulation Results (cont.)**

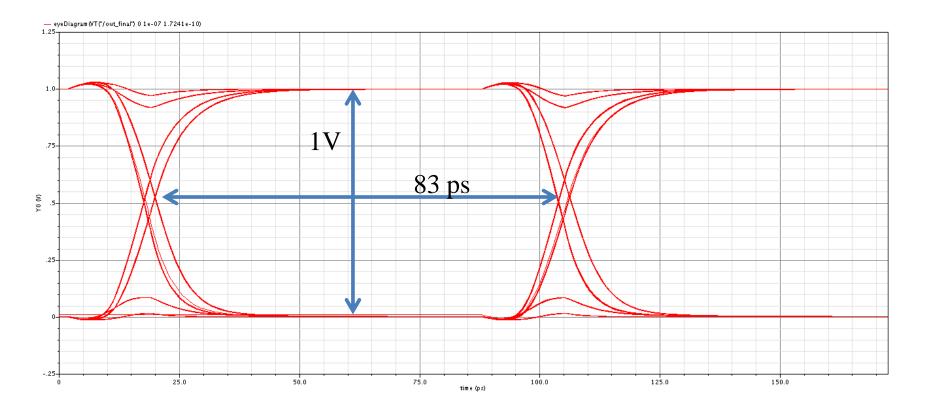

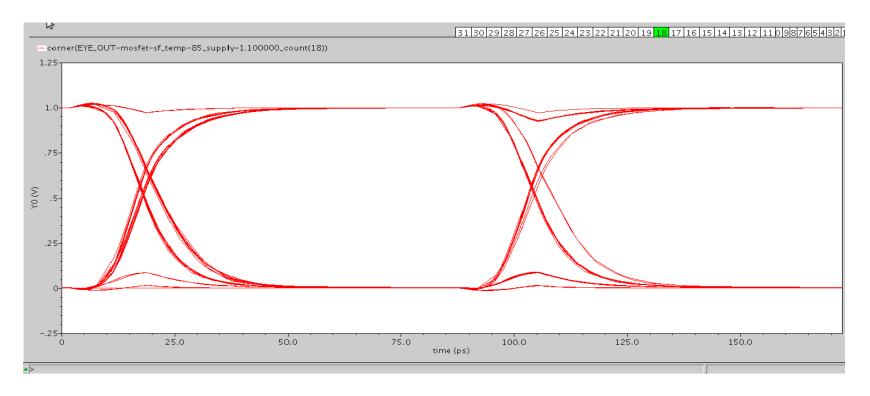

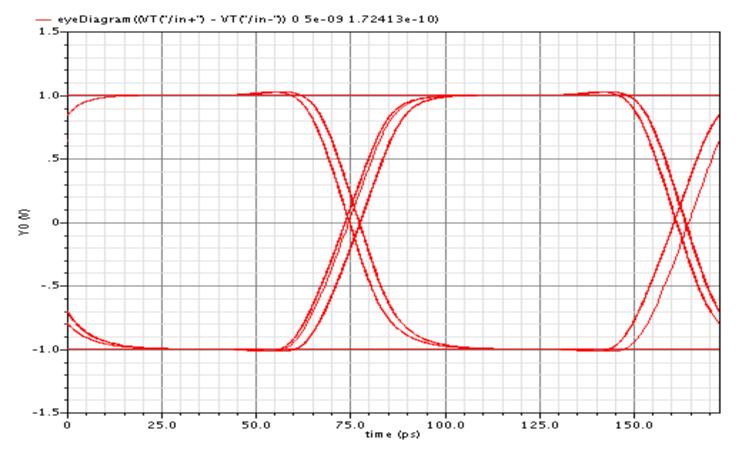

#### **Final Eyediagram**

#### **Corners Results :**

#### Worst case corner was at SF where eye opening is 82ps

## Layout

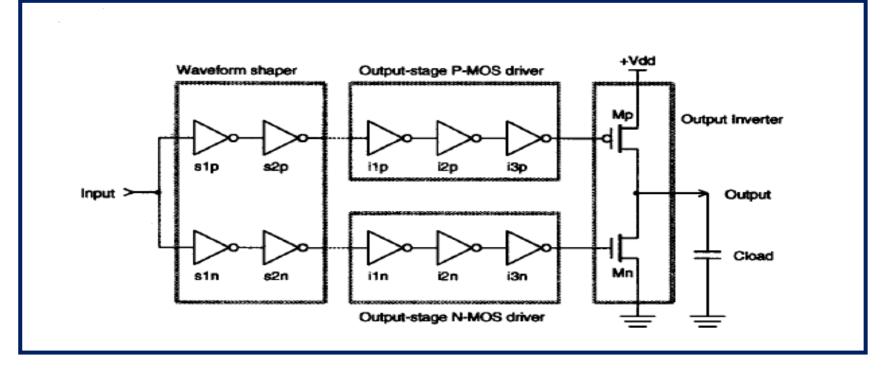

# Pre-driver

Presented by : Samar Hussein

### Outlines

- Why do we use a pre-driver?

- Power and delay problems in a pre-driver.

- Topologies of pre-driver buffers.

- Hand Analysis.

- Final design circuit and simulation outputs and Specs.

• A pre-driver is used between the driver and the multiplexer in the transmitter to drive the large capacitance of the driver without loading on the small capacitance of the multiplexer.

• a pre-driver acts as a buffering stage so it is implemented using a buffer series.

# Power problem in a pre-driver.

- A pre-driver face a problem with its large power consumption.

- Since a pre-driver is built up from a series of buffers "inverters" then it sinks a large current and is called " power hungry".

- This large current is a short circuit current occurring when both transistors of an inverter are on at same instant.

- this problem can be solved by limiting the number of buffers used.

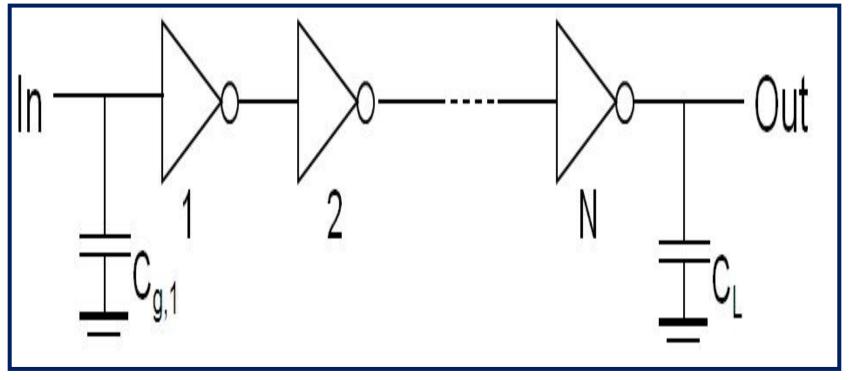

# Delay problem in a pre-driver.

• Buffers used in a pre-driver may introduce a delay which can cause its following stages not to work functionally.

• This delay can be minimized to an optimum value through a proper sizing of the inverters used in the buffering stages.

• F04 "fan out of 4" can be used to solve the delay problem in an optimum way.

# **Topologies of a pre-driver.**

Low power CMOS buffers

CML buffers

Tapered CMOS buffers

[Kei-Yong Khoo ; Integrated Circuits & Syst. Lab., California Univ., Los Angeles, CA, USA ; Wilson, A.N., Jr.]

6/7/2013

### CML buffers.

Payam Heydari, Ravi Mohavavelu,

Department of Electrical and Computer Engineering , University of California , Irvine, CA 92697-2625

[Integrated Circuits ECE481 Lecture 6 Inverter Chain Delay ,Mohamed Dessouky ,*Integrated Circuits Laboratory ,Ain Shams University ,Cairo, Egypt*]

### Hand Analysis.

•F = Cl/Cin

•Cl = 17fF, Cin = 0.5047fF. •Fopt =  $\sqrt[N]{F}$ •N =  $\frac{log(F)}{log(fopt)}$ •Where F = 33.683 , fopt = 4.

•Then we get Nopt = 3stages

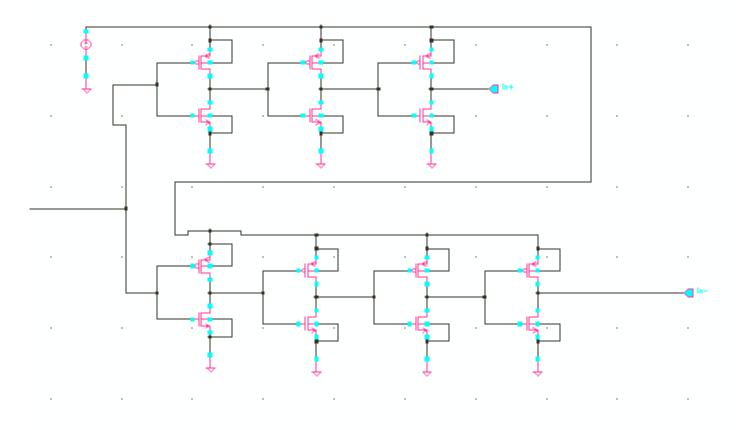

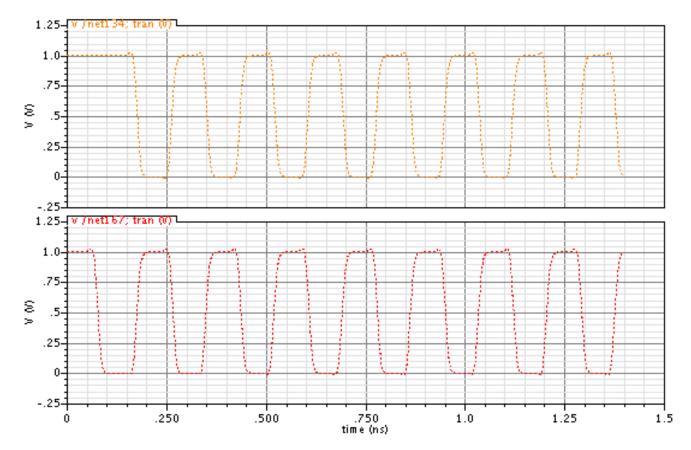

## Final design circuit.

### **Simulation Outputs.**

### Input Waveform

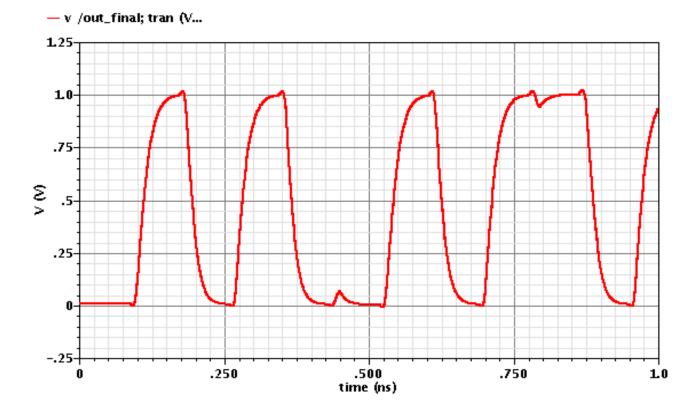

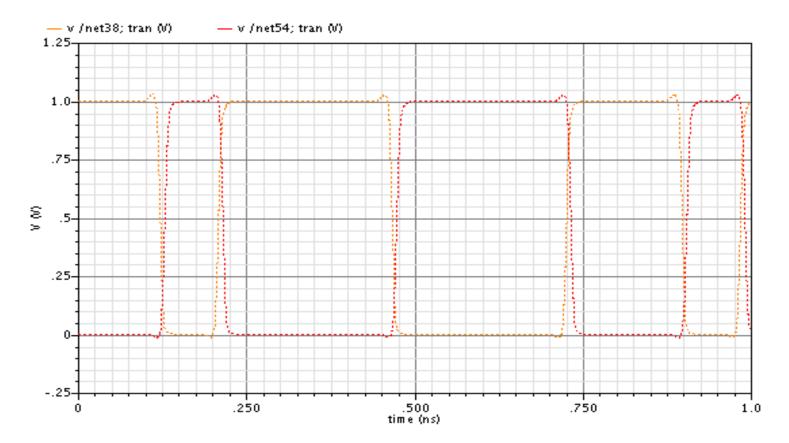

### **Output Waveform**

### Eye Diagram

### Input waveform.

#### **Transient Response**

### **Output waveform.**

Transient Response

# **Pre-driver Specifications.**

| Supply Voltage | 1 V    |

|----------------|--------|

| Supply Current | 0.4 mA |

| Power          | 0.4 mW |

# CML to CMOS Stage

Presented by : Samar Hussein

### **Outlines**

- Why do we need a CML to CMOS converter?

- Stages used in a CML to CMOS converter.

- Simulation results.

### Why do we need a CML to CMOS converter

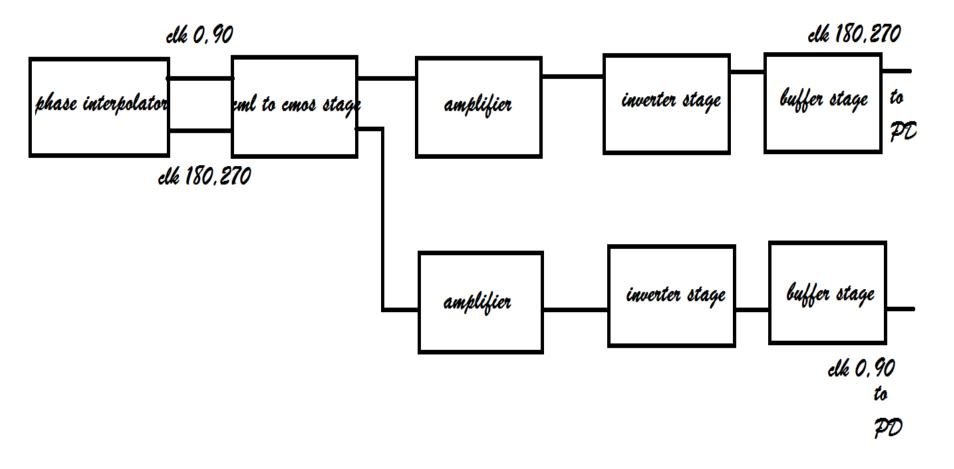

•A CML to CMOS converter is an intermediate block in the CDR loop between the phase interpolator and the PD.

• it converts the small swing output from the phase interpolator that uses CML circuits into a large swing that can drive the PDN and PUN CMOS circuits in the PD functionally.

•This avoids large power consumption and degradation in noise margins.

# Stages used in a CML to CMOS converter

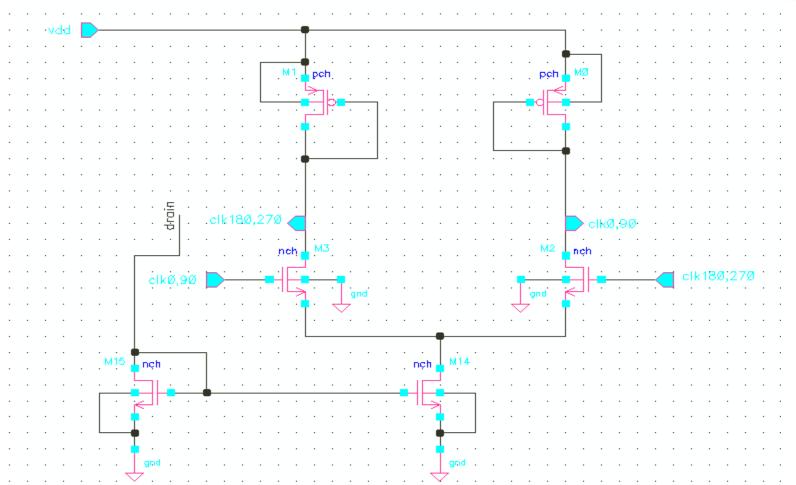

### **CML to CMOS stage**

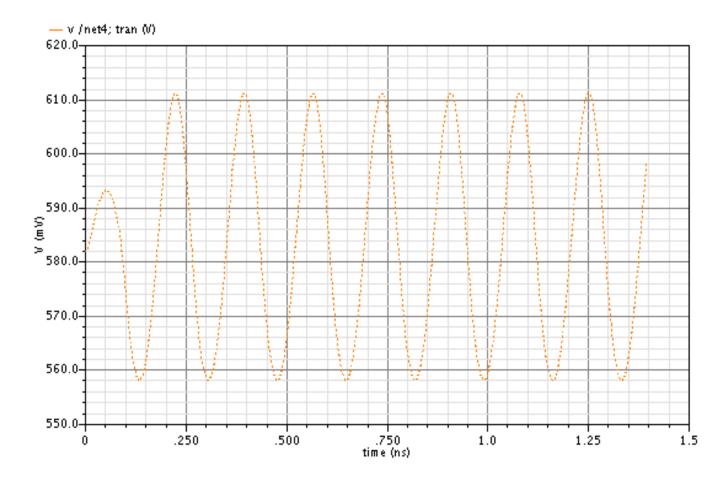

### **CML to CMOS stage output.**

**Transient Response**

### **Amplifier stage.**

| - |   |   |   |          |           | - | - | -     |      | -        | -        |     | - | - | - | -   | -   | -    |          |         |     | -                | -  |   | - |   |   | - | - |

|---|---|---|---|----------|-----------|---|---|-------|------|----------|----------|-----|---|---|---|-----|-----|------|----------|---------|-----|------------------|----|---|---|---|---|---|---|

| - | - |   |   |          | •         | - | - |       | -    | -        | -        | •   | - | - | - | •   | -   |      |          |         |     |                  |    |   | - |   |   |   | • |

| - | - |   |   |          | •         |   | - |       | -    | -        | -        |     | - |   |   |     |     |      |          |         |     | -                |    |   |   |   |   |   |   |

| - | - |   |   |          | •         |   | - |       | -    | •        |          |     |   |   |   |     |     |      |          | -       |     | -                |    |   |   |   |   |   | • |

| - | - |   |   | -        | •         |   | - | -     | -    | •        | •        |     | - |   | - | -   | •   |      | ·        | -       | -   | -                | •  | - |   |   |   |   | • |

| - | - |   | • |          | •         |   | - |       | -    | •        | •        | •   | - | • | - | -   | •   | -    | ·        | -       | -   | -                | •  | - | • |   |   |   | • |

| - | - |   | • |          | •         |   | - | -     |      | •        | · F      | a   |   | • | - |     | •   | 2    | ·        | · .     | •   |                  |    | - |   |   |   |   |   |

| - | - |   |   |          | •         |   |   | 'p.po | 1200 | °.       | •• "     |     | - |   |   |     | ppc | uywi | °. 🛉     | • · · · |     | -                |    |   |   |   |   |   |   |

|   | - |   |   | -        |           |   |   |       | -    | 3        | >        |     | - |   |   |     |     | -    | -        | >       | -   | -                |    |   |   |   |   |   |   |

| - | - |   |   | -        |           |   | - | -     | -    | 2        | ~        |     | - |   |   |     |     |      | 2        | ~       | -   | -                |    |   |   |   |   |   |   |

| - | - |   |   |          |           |   | - |       | -    | · •      | •        |     | - |   |   |     |     | -    | · •      | • •     |     | -                |    |   |   |   |   |   | • |

| - | - |   |   |          | •         |   | - | -     | -    | •        |          |     | - |   |   |     |     | -    | •        |         | · . | $\triangleright$ | àb |   |   |   |   |   |   |

|   | - |   |   | -        | •         |   |   | -     | -    | - • •    |          |     |   |   |   |     |     | -    | ٠٦       | · ·     | . • | -                | ΫÞ |   |   |   |   |   |   |

|   | - |   |   |          |           |   |   | -     |      |          | м        | 16  |   |   |   | ·   |     | ine  | :Hi 🚽    | ·M2     | .6  | -                |    |   |   |   |   |   |   |

| - | - |   |   |          | •         |   | - |       | ine  | :n       | ••••     | Ť   | - |   | - | ·   | •   | ГГ   | •        | -       |     | -                | •  | • |   |   |   |   | • |

| - | - |   | i | <u> </u> | $\square$ | • | - | •     | -1[  | •        | · .      | •   | - | • |   | . L | _   | ╘┥┠  | _        |         | Γ   | -                |    | • | • |   |   |   |   |

| - | - |   | - | -        |           |   | - |       | ·11  | ->       | -        | •   | - | · | • | •   | •   |      | 7        |         |     | -                | •  | • | • |   |   |   | • |

| - | - |   | • |          | •         |   | - |       | -    | · •      | <b>-</b> | •   | - | · |   |     | •   |      | •        | -       |     | -                |    | • | • |   |   |   |   |

| - | - |   | • | -        | •         |   | - |       | -    | 1        | •        | •   | - | • | • | •   | •   | -    | ·        | -       |     | -                | •  | • | • |   |   |   | • |

| - | - |   | • |          | •         |   | - | -     | -    | •        | •        | •   | - | • |   |     |     |      | - e      | · .     |     | -                |    | - | • |   |   |   |   |

| - | - | • | • | -        | •         | • | - | •     | -    | •        | -        | •   | - | • | - | •   | •   | -    | •        | •       | -   | -                | •  | • | • | • | • | • | • |

| - | - | • | • | •        | •         | • | - | -     | -    | •        | -        |     |   | • | - | -   | •   | •    |          | -       |     | -                | •  | - | • |   |   |   | • |

|   | - |   | • | -        | •         |   | • | -     | -    | <u>ب</u> | .gr      | 10. |   | • | - | •   | •   | -    | <u>ب</u> | .gno    | -   | -                |    | - | • |   |   |   |   |

|   | - | • | • | •        | •         | - | • | •     | •    |          |          | •   | - | • | - | -   | •   | -    | - ~      |         | -   | -                | •  | - | • | - | • |   |   |

|   | - |   | • | •        | •         | • | • |       | •    | -        | -        | •   |   | • | - | -   | •   | -    | -        | •       | -   | -                | •  | - | • |   |   | • |   |

|   | - | • | • | •        | •         | • | • | -     | -    | -        | •        | •   |   | • | - | -   | •   | •    | -        | •       | -   | -                | •  | - | • |   | • |   | • |

| - | - | - | - | -        | -         | - | - | -     | -    | -        | -        | -   | - | - | - | -   |     | -    | -        | -       | -   | -                | •  | - | - | - | - | - | - |

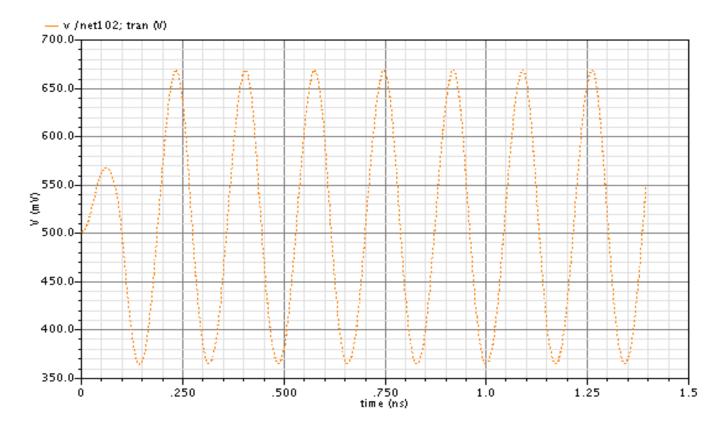

### **Amplifier stage output.**

**Transient Response**

### **Inverters and Buffer stages.**

### **Inverters output.**

#### Transient Response

### **Buffers output.**

#### **Transient Response**

### **Specifications:**

| Supply Voltage | 1 V     |

|----------------|---------|

| Supply Current | 7.75 mA |

| Power          | 7.75 mW |

### Driver

### Outlines

- Topologies of Driver

- LA & SA Driver

- Termination Control

- Final design circuit

- Simulation Outputs and Specs.

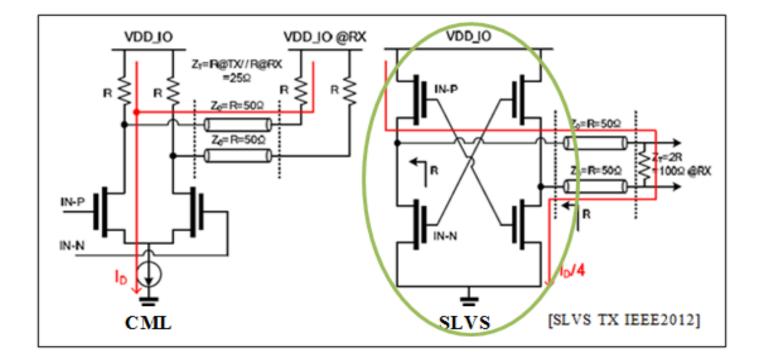

### **Topologies of Driver**

# SLVS consumes only 25% of the static output power of the CML

### LA & SA Driver

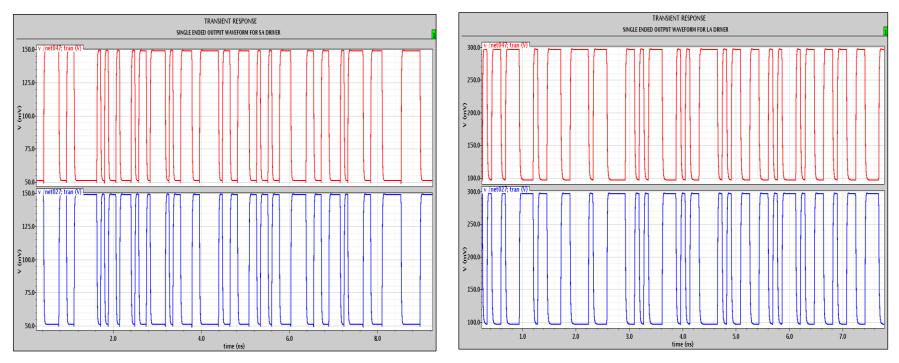

- Large amplitude  $\rightarrow$  Vdd=0.4V

- Small amplitude  $\rightarrow$  Vdd =0.2V

- For low-swing (<400-500mVpp), an all NMOS driver is suitable

- For high-swing, CMOS driver is used.

### Advantages of low swing driver:

- Higher speed  $\rightarrow$  Devices switch faster.

- Smaller device  $\rightarrow$  Lower capacitance.

- Better linearity → Driver transistor stays in a single region of operation when ON.

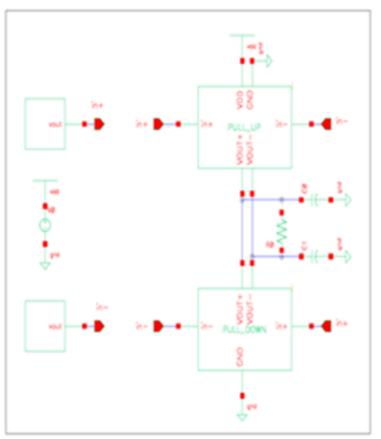

### **Termination Control**

- Segmented Driver → implementation depends on output swing requirements but as supply voltage changes, the implementation does not change; only the number of segments differs to achieve matching.

- The resistance provided by the mosfets vary across the process corners so we need to calibrate the termination in order to reduce signal reflections.

- The termination circuit consist of 22 fixed segments and 78 controllable unit segments tied together for pull up network and 23 controllable unit segments tied together for pull down network. The fixed segments are always turned on, and other unit segments will be set by calibration.

### **Final design circuit**

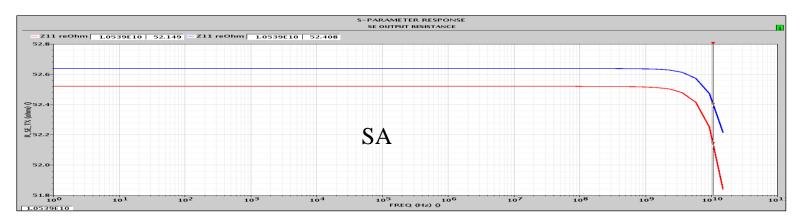

# **Simulation Outputs and Specs**

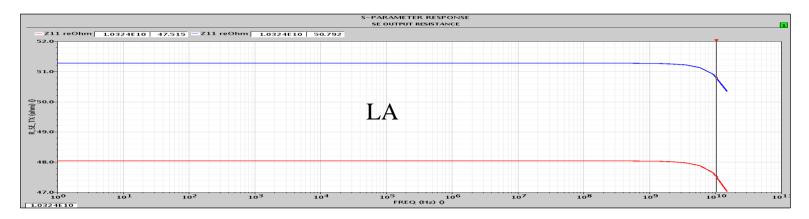

- RSE\_TX (Single ended output resistance) in the range from 40  $\Omega$  up to 60  $\Omega$ .

- $\Delta RSE_TX$  (Output resistance mismatch) is 6  $\Omega$ .

### Simulation Outputs and Specs(cont.)

| Symbol                       | MIN    | MAX    |

|------------------------------|--------|--------|

| V <sub>DIF_DC_LA_Rt_TX</sub> | 160mV  | 240 mV |

| V <sub>DIF_DC_SA_Rt_TX</sub> | 100 mV | 130 mV |

| V <sub>CM LA TX</sub>        | 160 mV | 260 mV |

| V <sub>CM SA TX</sub>        | 80 mV  | 190 mV |

SA

LA

### Simulation Outputs and Specs(cont.)

### **Simulation Outputs and**

### Specs(cont.)

### Simulations Outputs and Specs(cont.)

|         | SA    | LA    |

|---------|-------|-------|

| VDD     | 0.2V  | 0.4V  |

| Current | 1mA   | 2mA   |

| Power   | 200µW | 800µW |

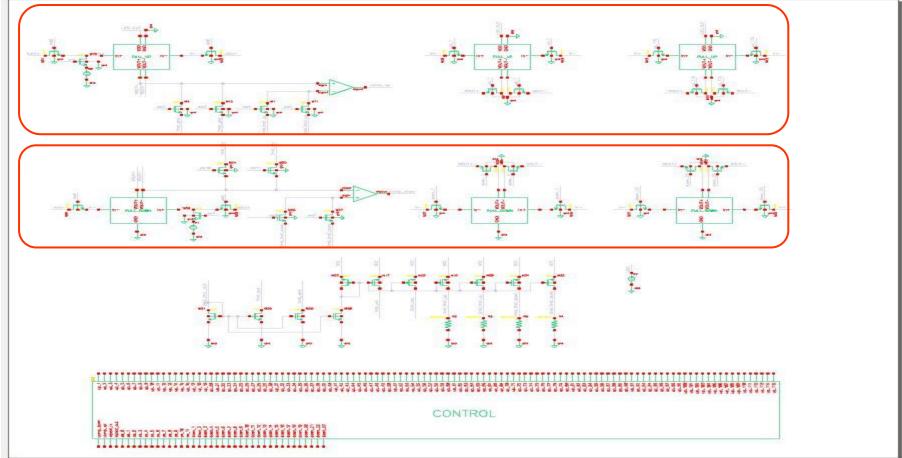

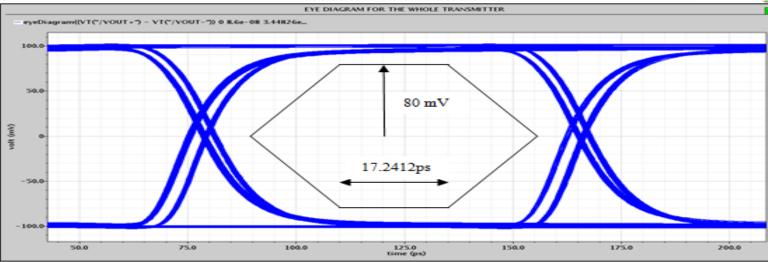

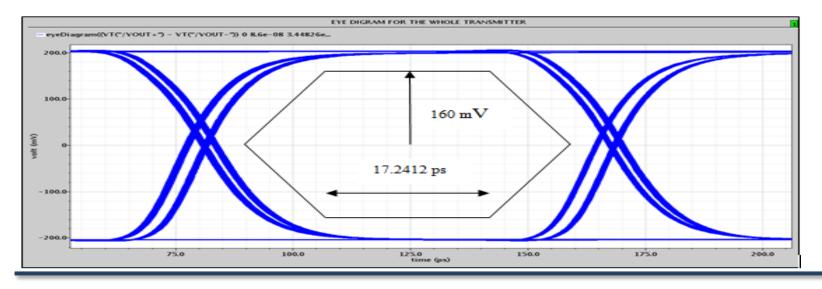

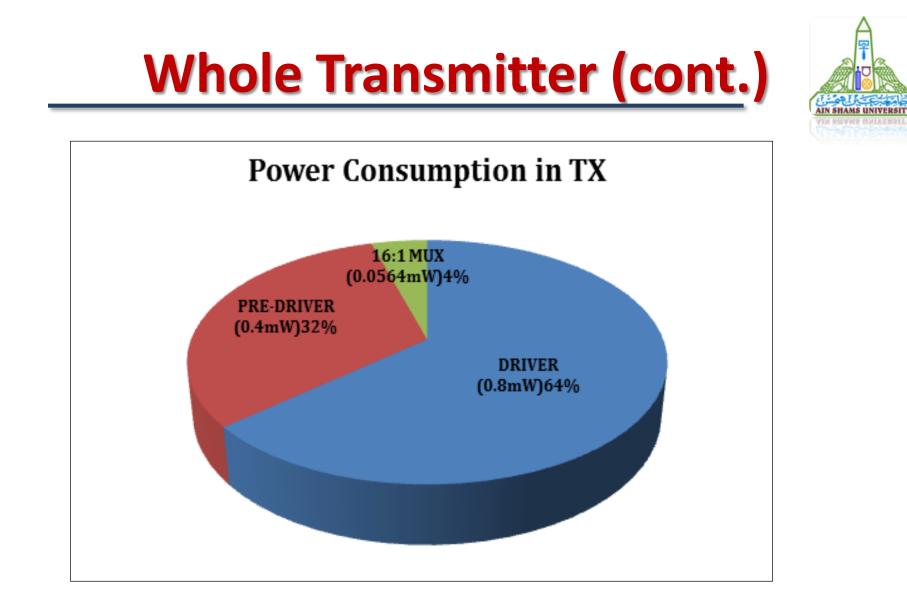

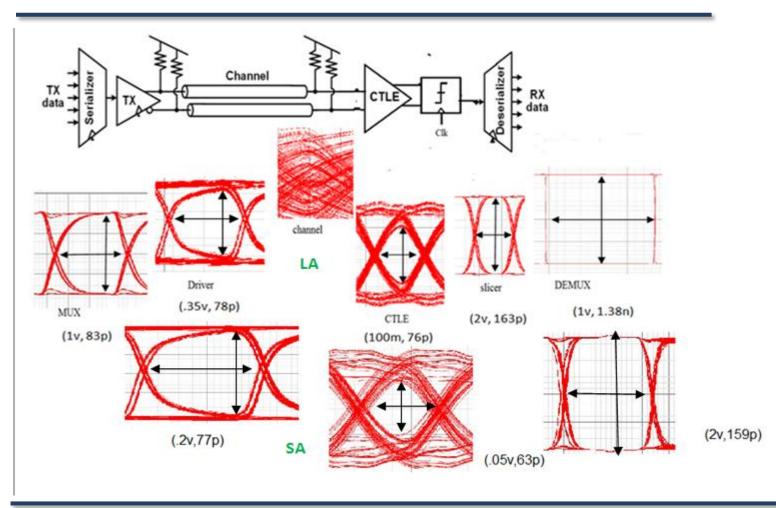

# **Whole Transmitter**

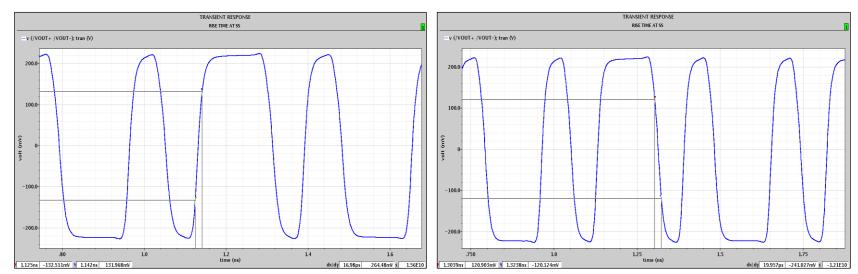

## Whole Transmitter (cont.)

## Whole Transmitter (cont.)

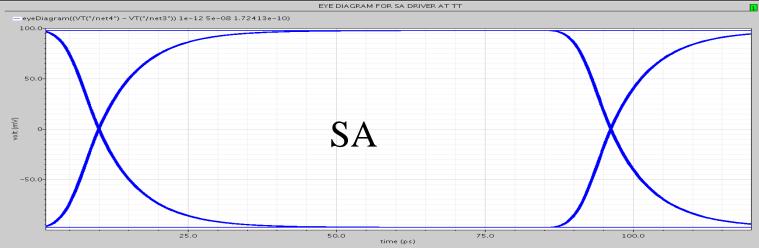

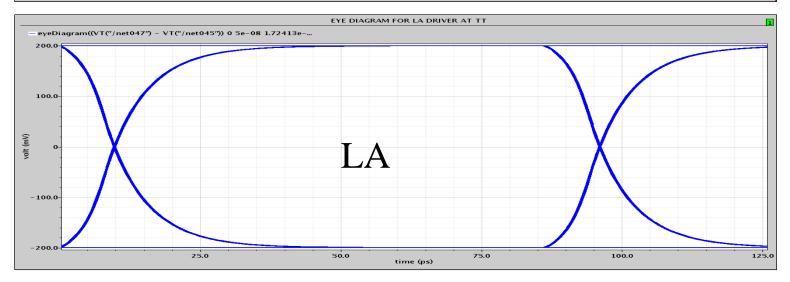

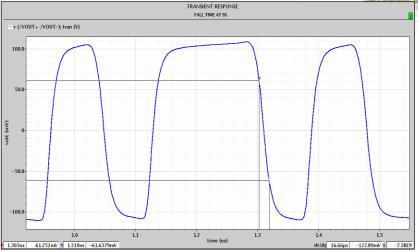

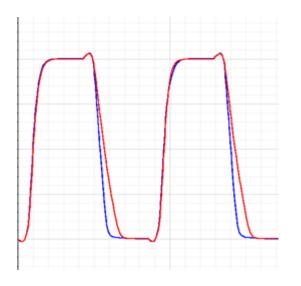

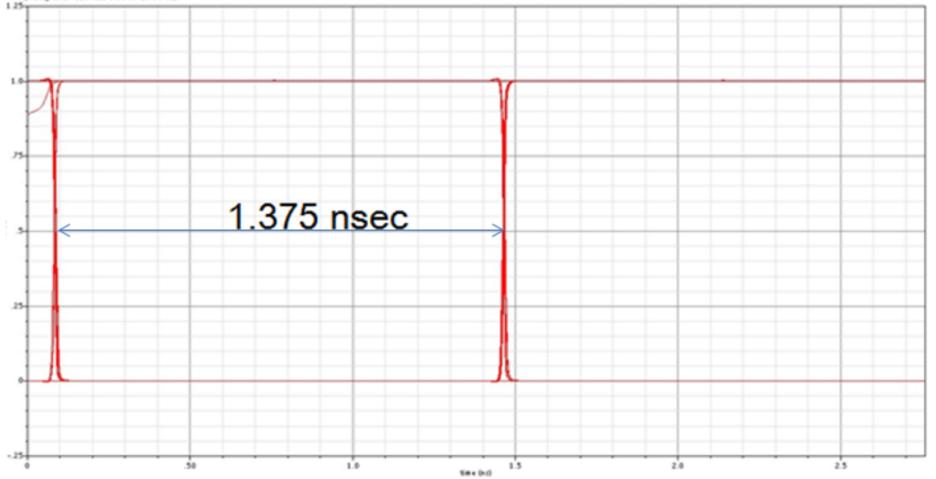

- Rise and Fall times are defined as transition times between the 20% and 80% signal levels of the differential output

- Rise and Fall time = 0.2 UI

| Corner | Amplitude | Rise Time (ps) | Fall Time (ps) |

|--------|-----------|----------------|----------------|

| TT     | SA        | 13.172         | 14.242         |

| SS     | SA        | 14.79          | 16.66          |

| TT     | LA        | 12.9291        | 17.218         |

| SS     | LA        | 16.98          | 19.957         |

## Whole Transmitter (cont.)

## Receiver

#### Outlines

- Introduction.

- Termination.

- Variable gain amplifier.

- Continues time linear equalizer.

- CDR.

- Phase Detector and Charge Pump (PD and CP).

- Analog Phase Interpolator (PI).

- De-Serializer.

# **Receiver Termination**

Presented by : Mohamed Mohie

## introduction

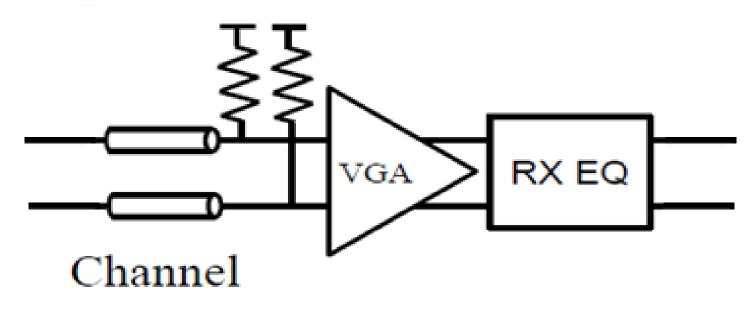

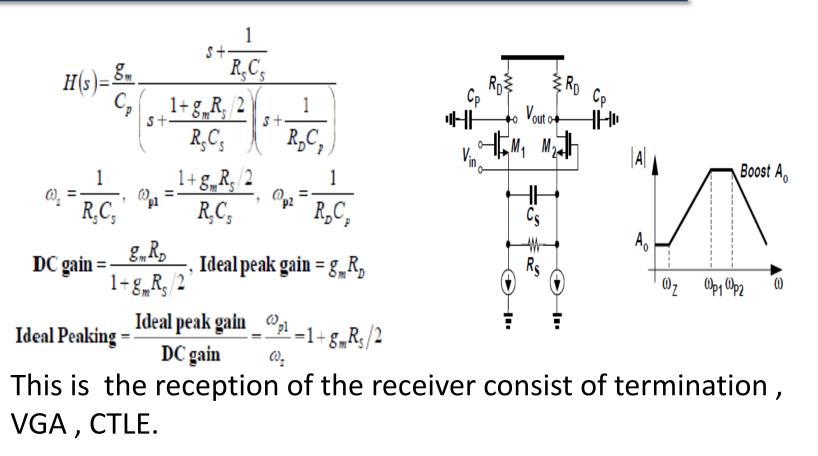

# This is the reception of the receiver consist of termination , VGA , CTLE.

## **Outlines**

Introduction

topologies

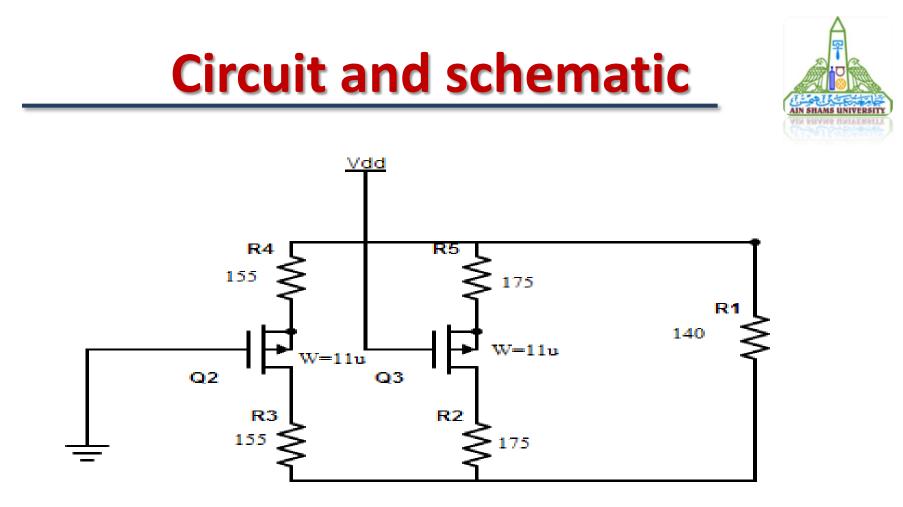

Circuit and schematic

Simulations and results

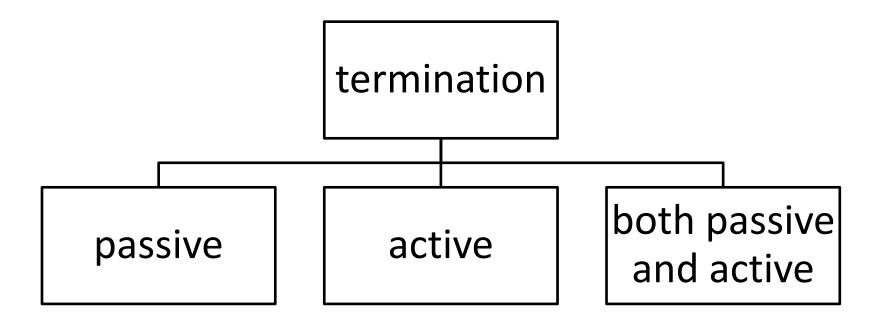

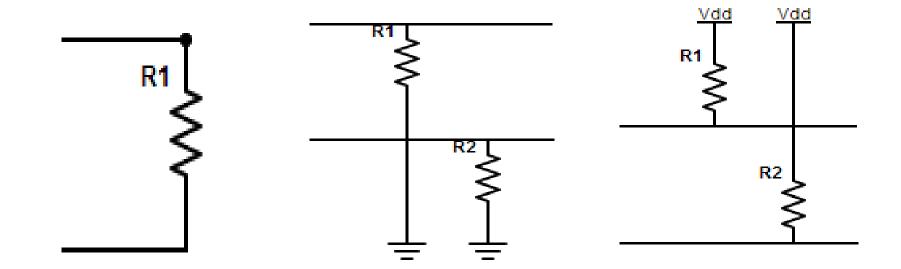

Passive: consist of resistance Active : consist of transistors

Differential resistance

resistance to Gnd

resistance to Vdd

it's a differential termination consist of resistance and transistors where the transistors are used as on/off switch

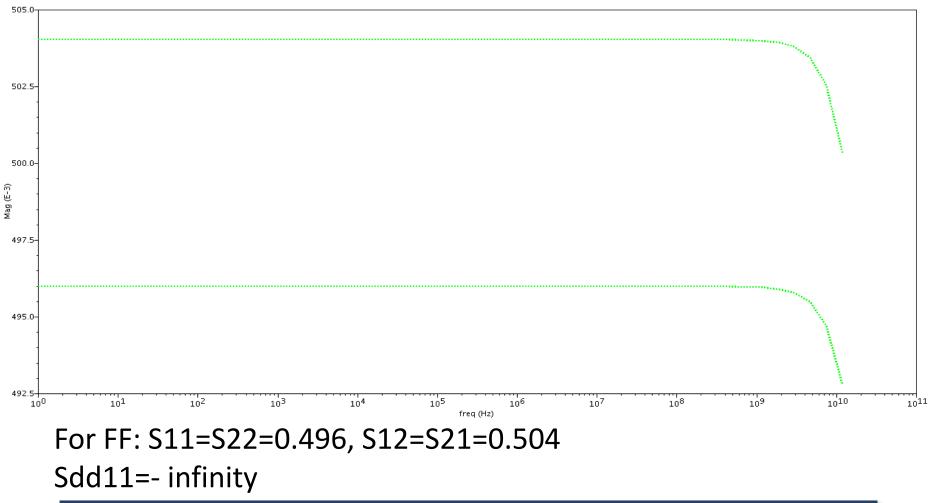

- Since we use differential termination we calculate

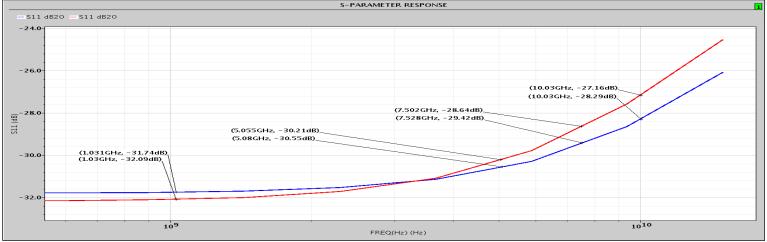

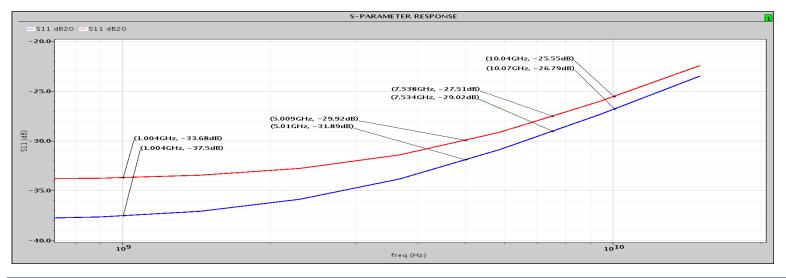

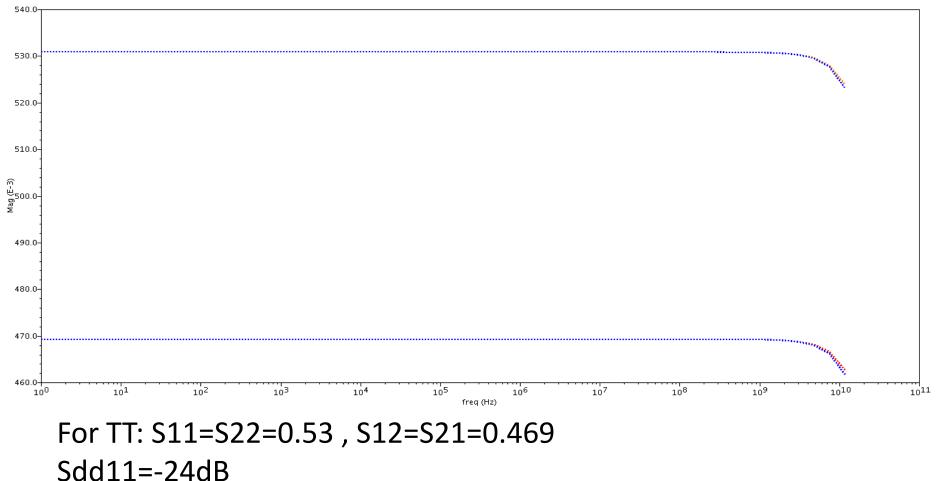

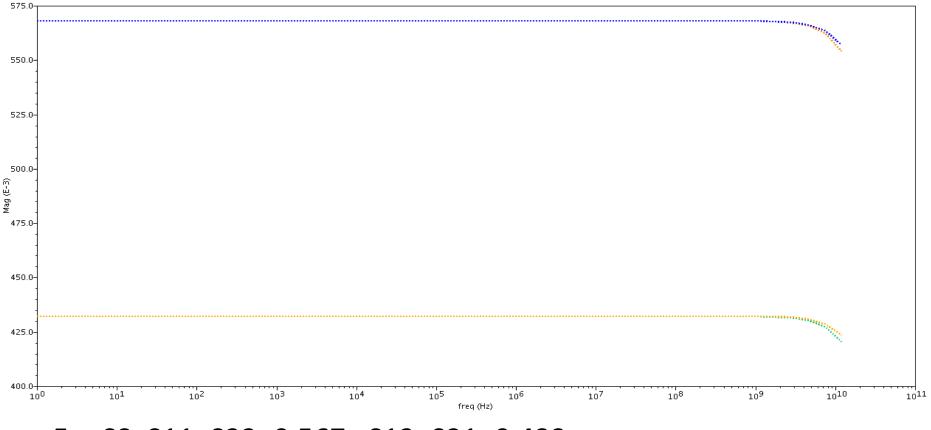

Sdd11 instead of S11

- Sdd11=1/2(s11-s12-s21-s22)

S-Parameter Response

S-Parameter Response

#### For SS: S11=S22=0.567 , S12=S21=0.432 Sdd11=-23.4dB

S-Parameter Response

# Variable Gain Amplifier (VGA)

Presented by : Mohamed Mohie

## **Outlines**

Introduction

Circuit and schematic

Simulations and results

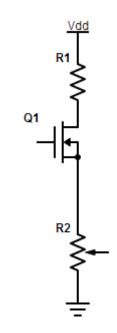

•By changing RS we get different values of gain

amplifier

of gain and it also can make attenuation

•We use a source degeneration common source

•The variable gain amplifier gives different values

• it's  $gain = \frac{-gm Rout}{1 + gm RS}$

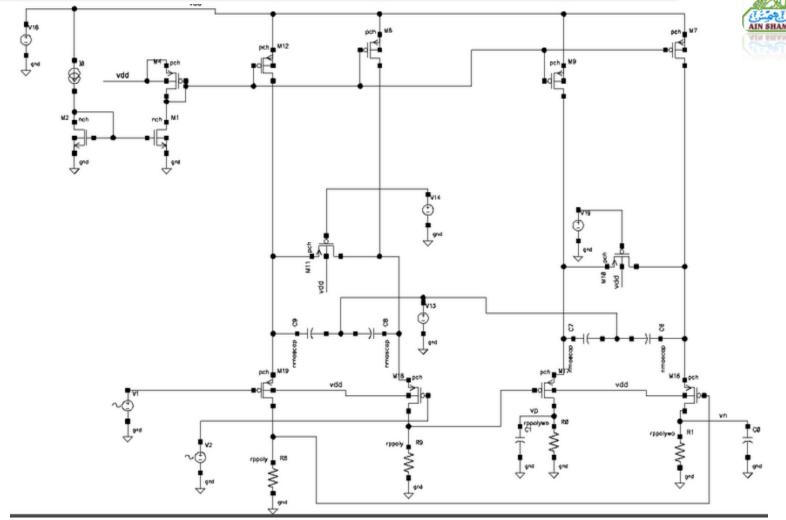

## **Circuit and schematic**

## **Circuit and schematic**

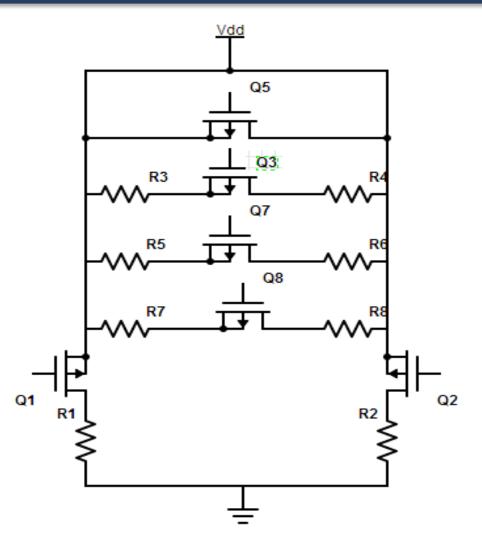

• When Q5 or Q3 or Q7 or Q8 are switched on the circuit gives a certain gain or a certain attenuation , and we can open more than one switch at a time getting more values of gains and attenuations

- This VGA gives range from 5.75dB to -4dB

- The dc input ranges from 25mV to 330mV gives output 200mV

130

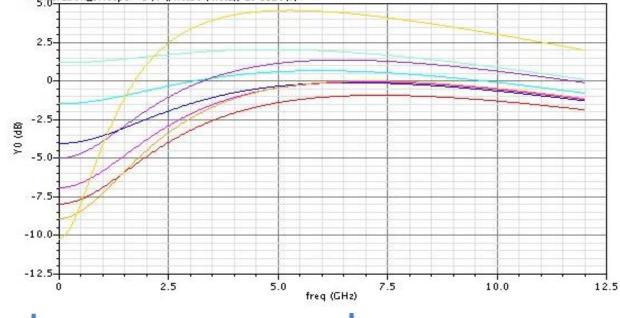

AC Response

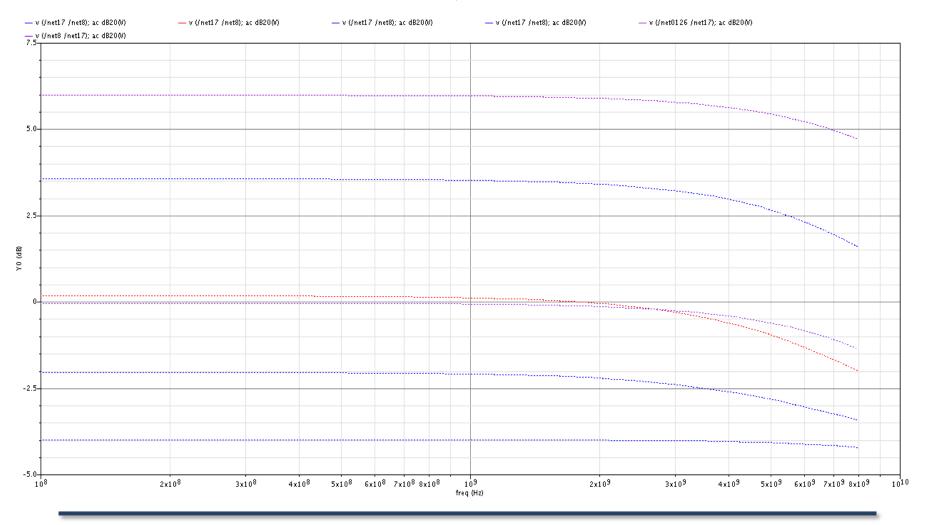

## CTLE (Receiver Equalization)

Presented by : Reem Amr

## Outlines

- Receiver Equalization

- CTLE

- CTLE output

- Composing Receiver circuits

- Verification for correct data from slicer

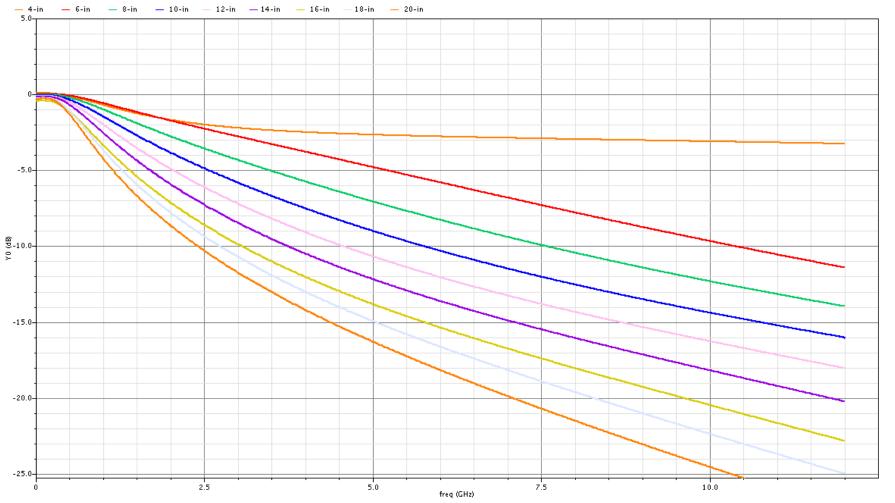

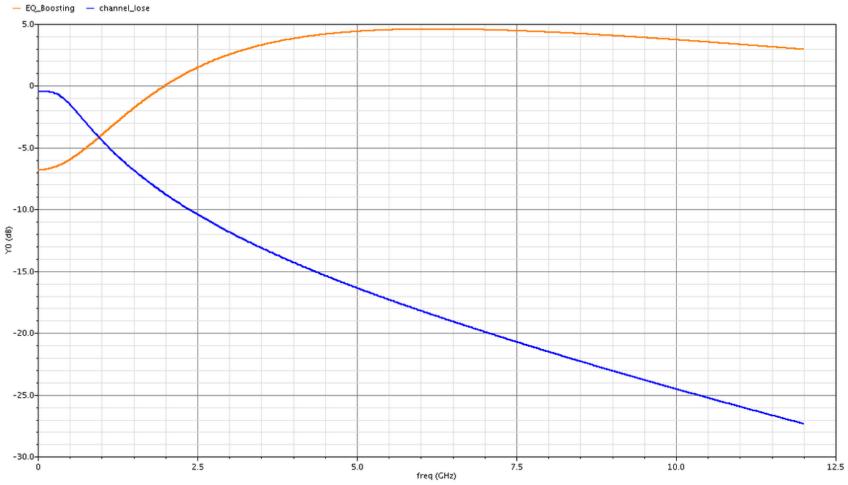

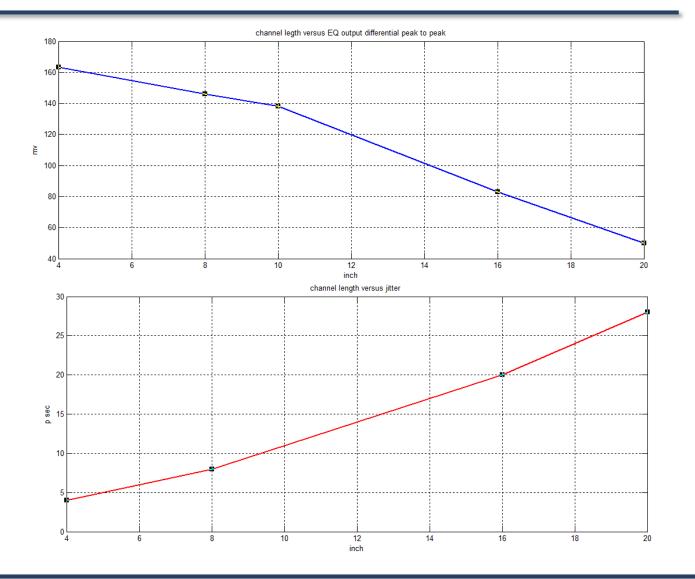

## **Receiver Equalization**

- Received signal suffers frequency dependent losses .

- To cancel Inter symbol interference (ISI) due dispersion and skin effect.

## Continuous Time linear Equalizer [CTLE]

## **Schematic**

## **Channel losses**

7/10/12013

#### **CTLE outputs**

| Channel | Rs    | Cs   | Boost  |  |

|---------|-------|------|--------|--|

| (in)    |       | (fF) | factor |  |

|         |       |      | (dB)   |  |

| 4       | 430   | 125  | 3      |  |

| 6       | 645   | 104  | 4      |  |

| 8       | 950   | 94   | 5.5    |  |

| 10      | 1.1K  | 115  | 7      |  |

| 12      | 1.5K  | 94   | 8      |  |

| 14      | 1.8K  | 84   | 9.5    |  |

| 16      | 2.15K | 94   | 11     |  |

| 20      | 2.8K  | 183  | 14     |  |

#### For 20-inch channel

## outputs

AIN SHAMS UNIVERSITY

## **Outputs**

####

#### 7/10/2013

## Outputs

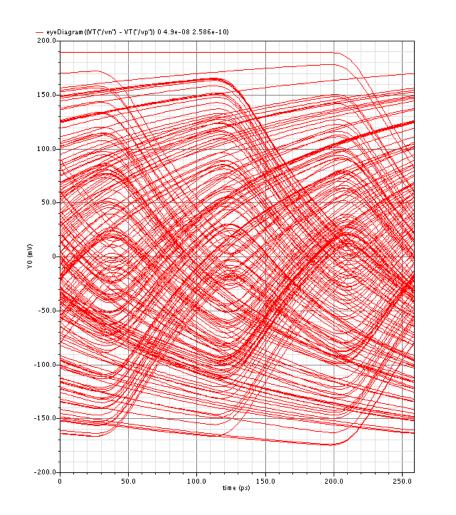

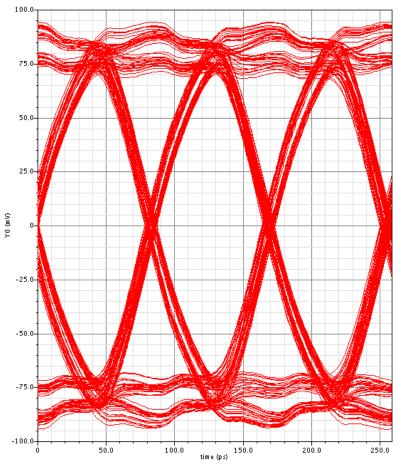

## Verification for correct data from slice

- When composing EQ with slicer

- With 6psec clock jitter, We got 0.5UI margin for clock and data to be delayed.

## When composing transmitter and recei circuits

AIN SHAMS UNIVERS

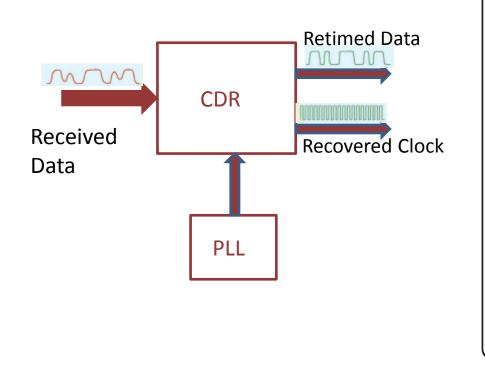

# Clock and Data Recovery (CDR)

Presented by : Eman Omar

#### Outlines

- CDR

- CDR Topologies

- Selected Topology

#### CDR

- Function of CDR

- Requirements of CDR

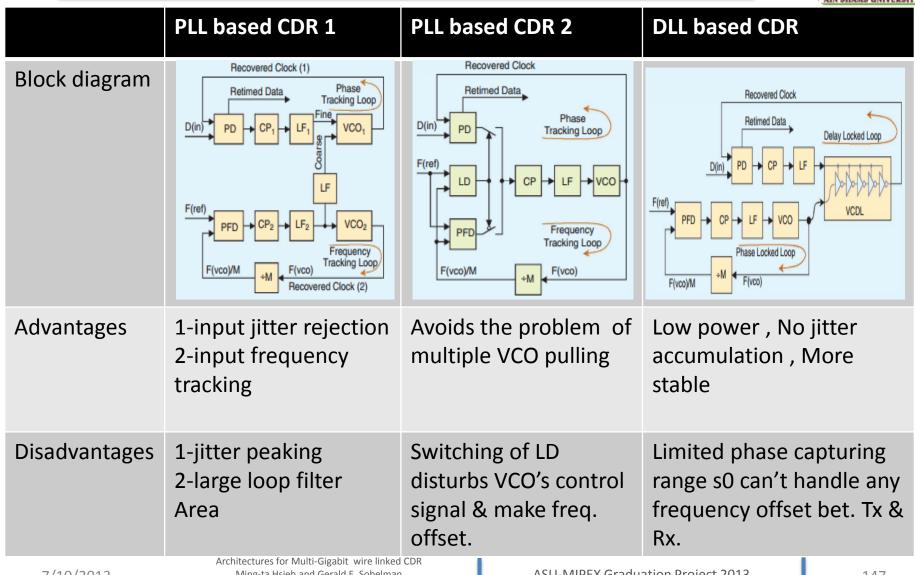

### **CDR Topologies**

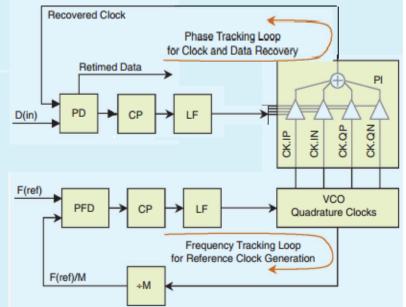

### Selected Topology PI based CDR

- Solves the Problem of limited capturing range of DLL based CDR

- Half rate topology

- Analog PI

#### Advantages:

Multichannel Share Input Clocks.

high resolution so less jitter.

### Phase Detector and Charge Pump (PD and CP)

Presented by : Eman Omar

#### Outlines

- Phase Detector

- Selected Topology

- Slicer

- XOR

- Multiplexer

- PD Results

- Charge Pump

- Selected Topology

- Simulation Results

### Phase Detector Linear and Binary PD

|                | Linear PD                                                | Binary PD                                                                                                                                    |

|----------------|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Output signals | Provide both phase and magnitude of the phase difference | Provide only the phase of the phase difference                                                                                               |

| Advantages     | Small output jitter                                      | <ul><li>1-Less sensitive to data</li><li>patterns</li><li>2-Power efficient than</li><li>linear at high speed</li><li>applications</li></ul> |

| Disadvantages  | Non linearity for non<br>uniform data patterns           | High output jitter                                                                                                                           |

| Gain           | Pulse<br>width<br>UP<br>DOWN<br>-180° Δφ                 | T<br>-180°<br>Pulse<br>Width<br>UP-DOWN<br>+180°<br>Δφ                                                                                       |

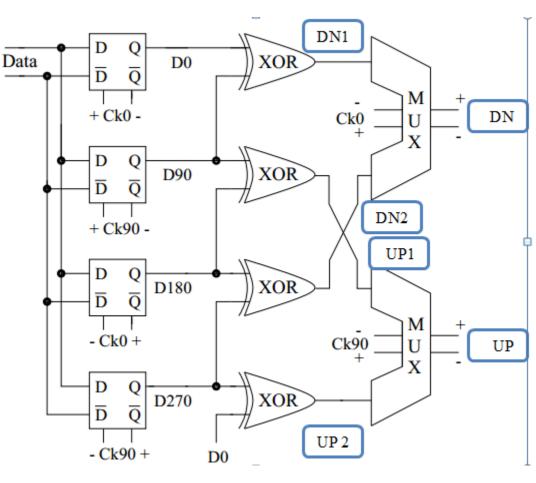

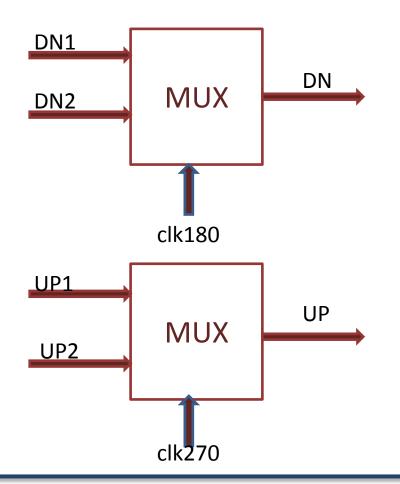

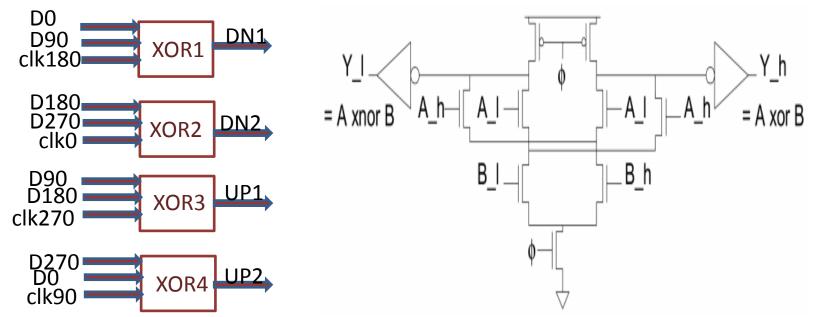

### Selected Topology Half Rate Alexander PD

- Uses I & Q clock phases.

- Has two data slicers & two edge slicers.

7/10/2013

### Half Rate Alexander PD (cont.)

Constant current , BUT PTAT PTAT current increase with 1.175.00.00 tability Seed. Biller of the OTA Depending PSB

$$DN_2 = D_{180} + D_{270} \qquad DN_1 = D_0 + D_{90}$$

$$UP_2 = D_{270} + D_0 \qquad UP_1 = D_{90} + D_{180}$$

**Clock early**

| 90 → 360             | 90 → 360      |

|----------------------|---------------|

| 270→ 360+180         | 270→ 360+180  |

| <b>180 → 360 +90</b> | 180 → 360 +90 |

| 0 → 270              | 0 → 270       |

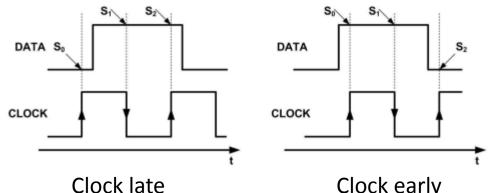

Half Rate Alexander PD (cont.)

Mux clock phases to eliminate the delay from slicer:

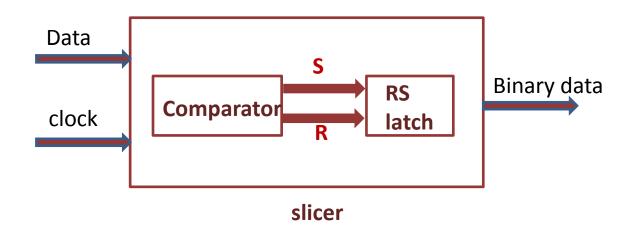

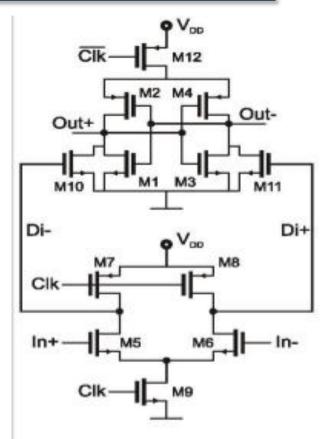

Slicer is a dynamic comparator followed by an RS latch

## Slicer (cont.)

#### **Comparator:**

|               | Strong Arm                                                                                                                                                                                                                                                               | Double tail                                                                                                                            |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|

| Advantages    | 1- lower power<br>consumption.                                                                                                                                                                                                                                           | <ol> <li>requires small voltage<br/>headroom.</li> <li>separation of the input tail<br/>current and the latch tail current.</li> </ol> |  |

| Disadvantages | <ol> <li>requires large voltage<br/>headroom.</li> <li>shows very strong<br/>dependency on speed with<br/>different common mode<br/>input voltages.</li> <li>tradeoff between the<br/>latch's speed and the time<br/>the gain stage remain in<br/>saturation.</li> </ol> | <ul><li>1-Higher power consumption.</li><li>2-requires clock and clock bar.</li></ul>                                                  |  |

### Slicer (cont.) Double Tail Voltage SA

1- Operation .

2- Sizing Consideration.

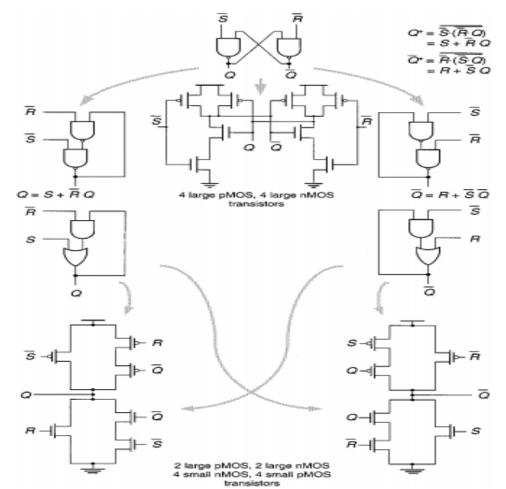

#### Slicer (cont.) RS Latch

$Q^{+} = S + \overline{R}. Q$  $\overline{Q}^{+} = R + \overline{S}. \overline{Q}$

7/10/2013 Improved Sense-Amplifier-Based Flip Flop Design & measurements

#### Slicer (cont.) Results:

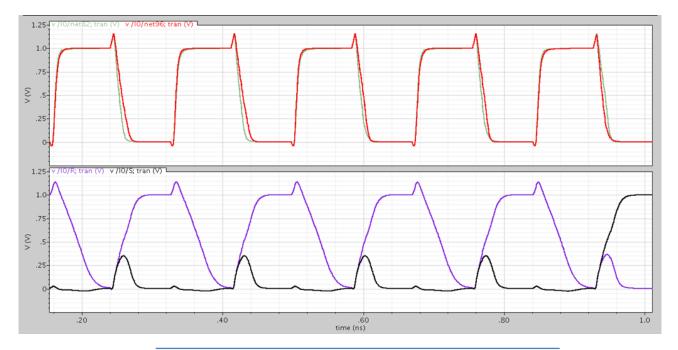

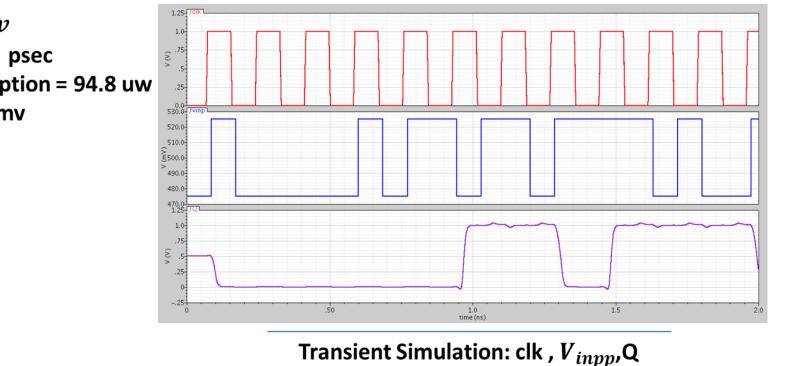

Transient Simulation : $D_i^+$ ,  $D_i^-$ , R,S

#### 160

$V_{inpp} = 50 mv$ **Delay = 40.775 psec** Power consumption = 94.8 uw Sensitivity = 4 mv

#### Slicer (cont.) **Results (cont.)**

#### Slicer (cont.) Results (cont.)

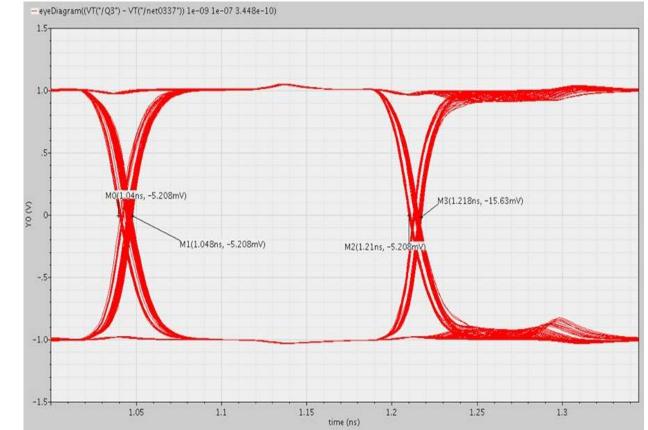

#### Eye Diagram of slicer output

- Eye opening = 162 psec

7/10/2013

### Slicer (cont.) Results (cont.)

# AIN SHAMS UNIVERSITY

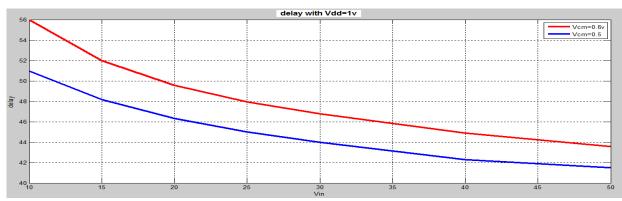

#### Sweeping $\Delta Vin$ for the same vdd = 1v with diff $V_{cm}$

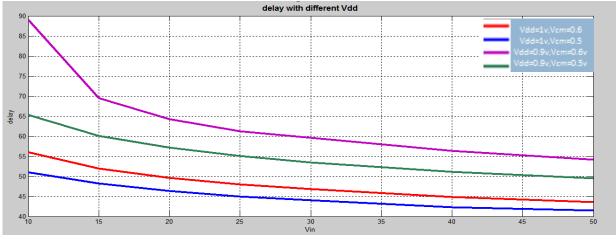

#### Delay for different vdd:

#### It's disadvantage to the PD system .

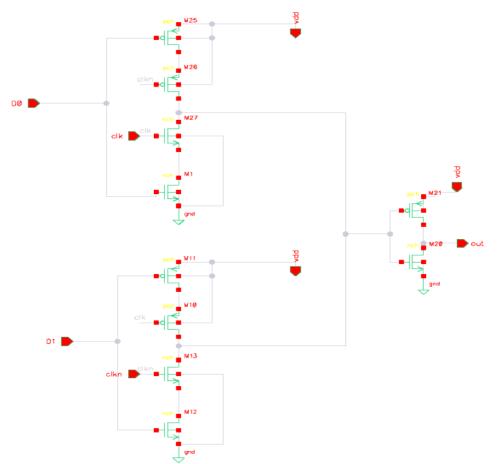

XOR

**Dynamic XOR**

Supports the 5GHZ speed.

#### Multiplexer

#### **Multiplexer Topology:**

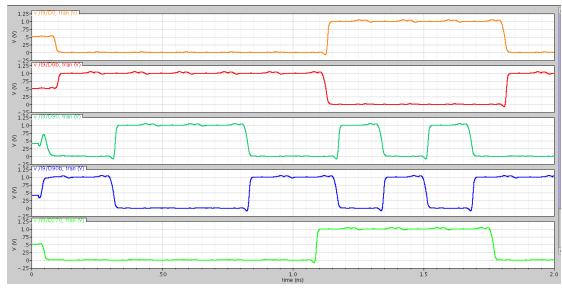

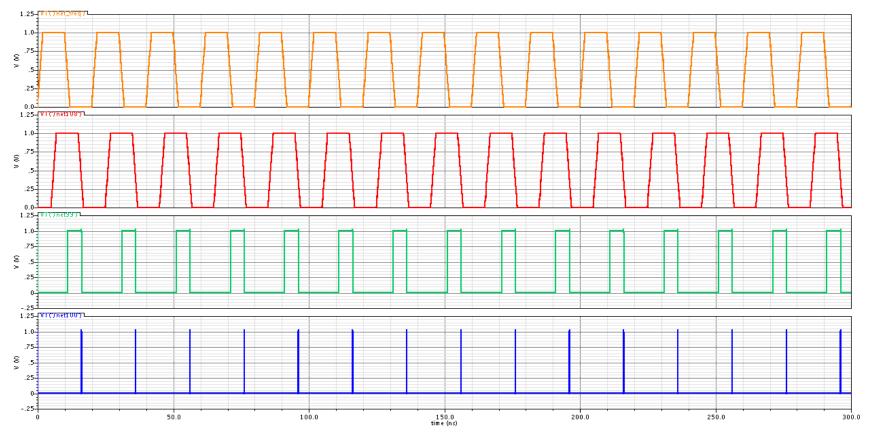

#### **PD Results**

Total power of PD = 604.159 uw.

#### Example:

The clock is late by 30 psec.

#### <u>1- slicer output:</u>

D0, D90, D180, D270

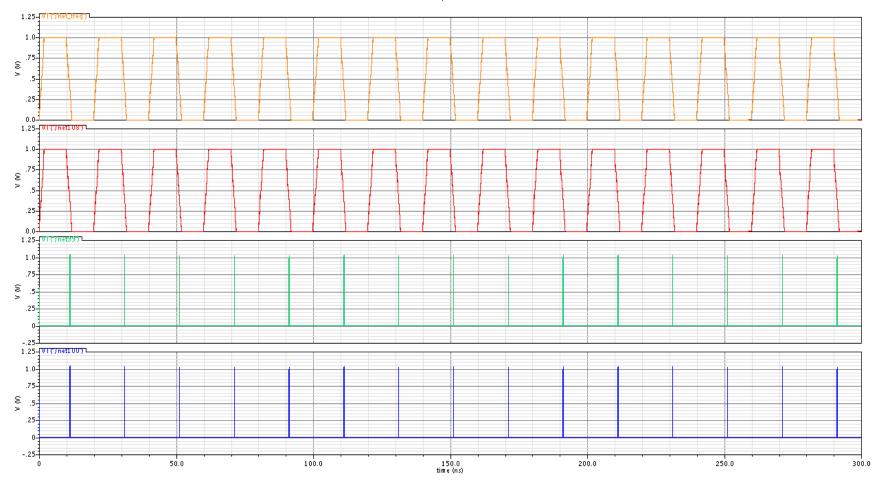

### PD Results (cont.)

#### 2-output of Mux :

UP,DN

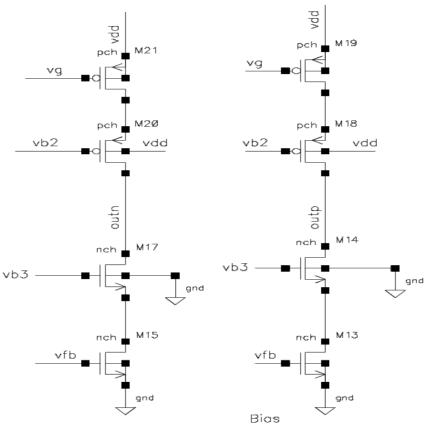

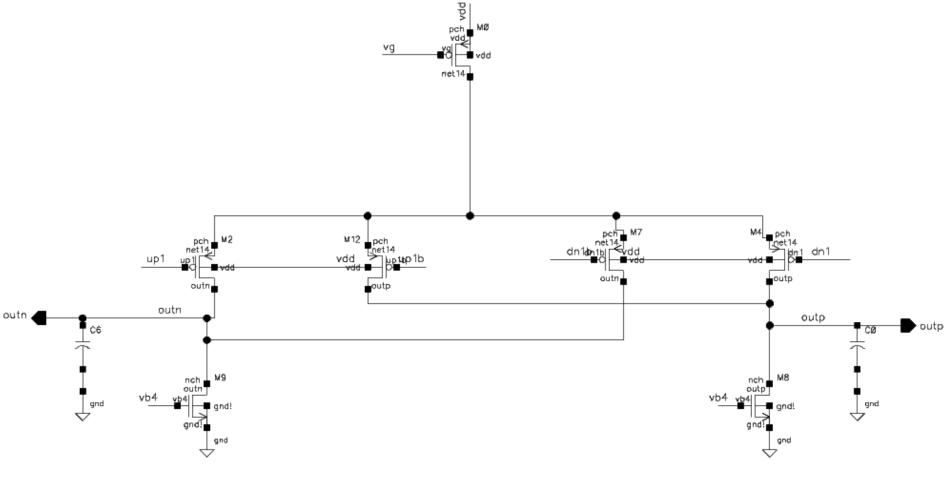

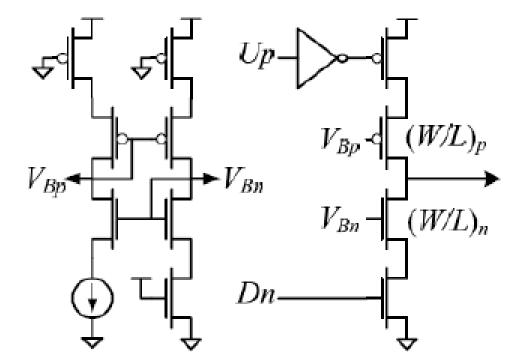

#### **Charge Pump**

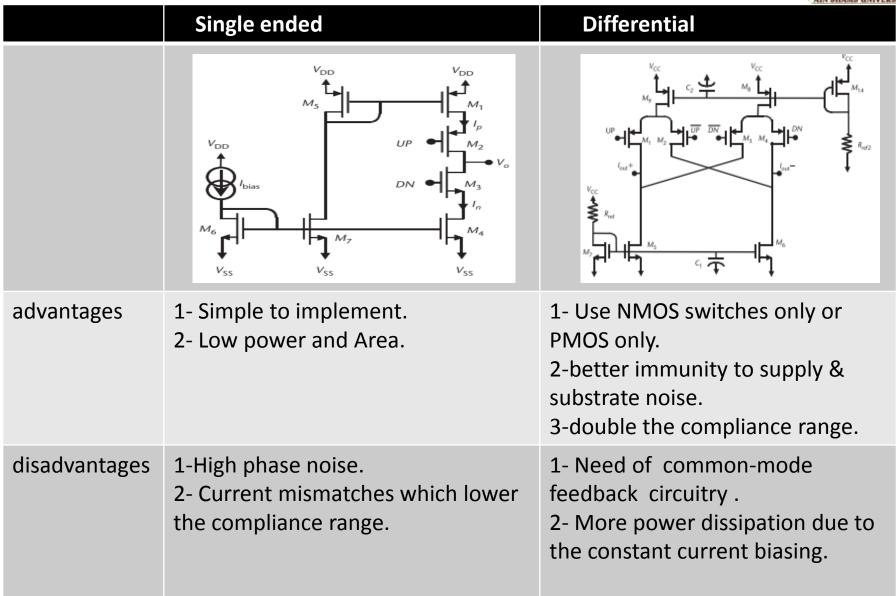

### **Selected Topology**

- Selected Filter

- Biasing the output common mode voltage

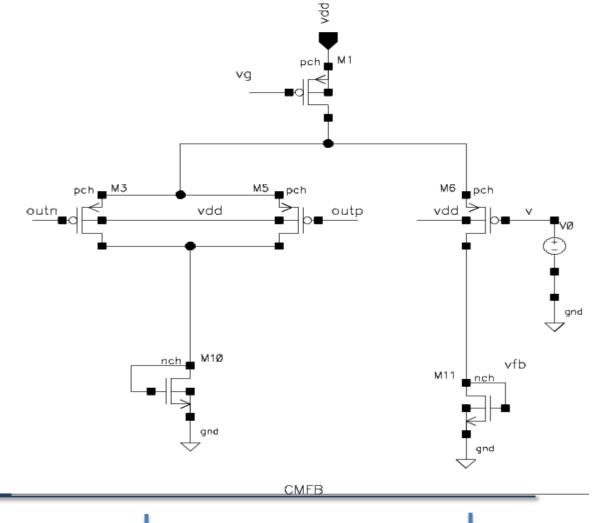

- Uses a CMFB circuit.

#### **Selected Topology**

charge pump

### **Selected Topology (cont.)**

#### Common mode feedback circuit:

### **Selected Topology (cont.)**

Switch circuit:

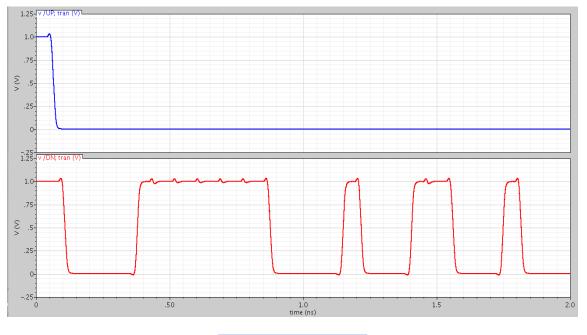

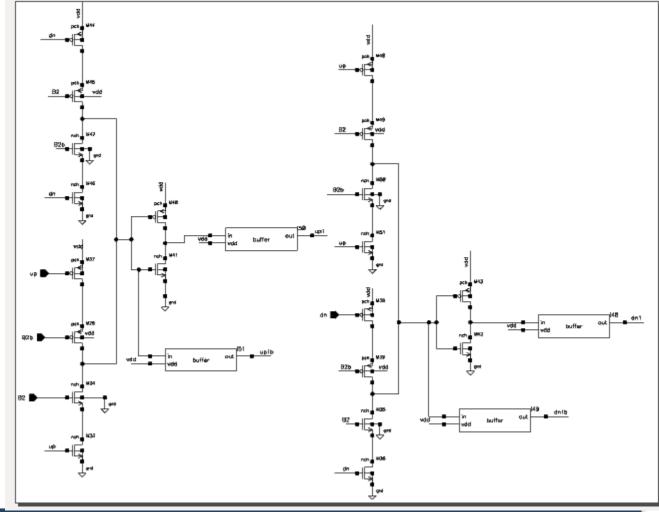

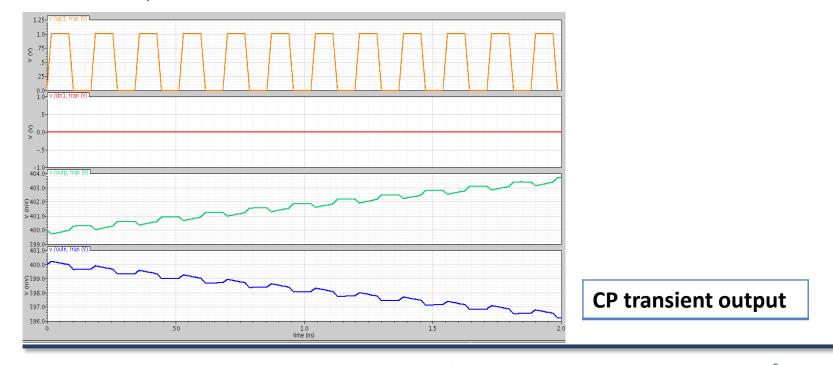

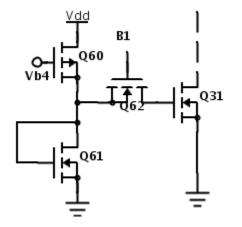

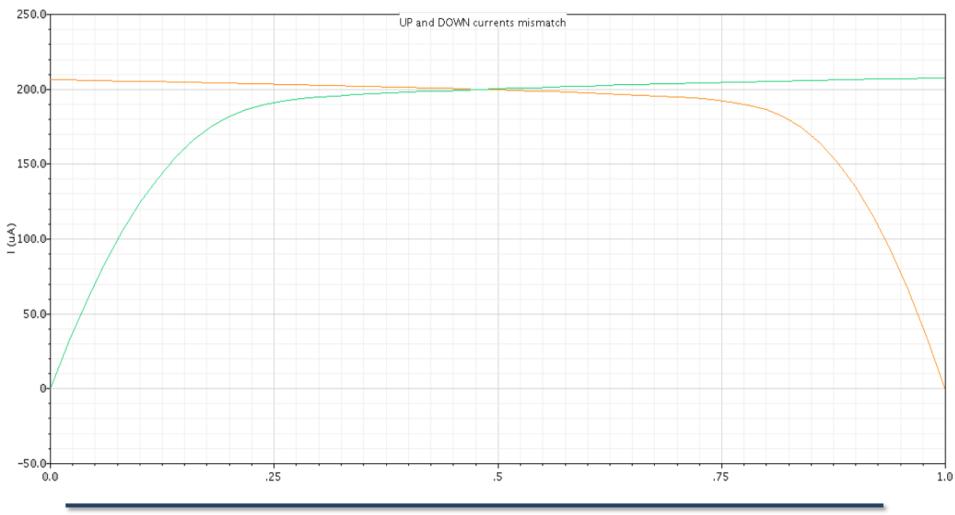

#### **Simulation Results**

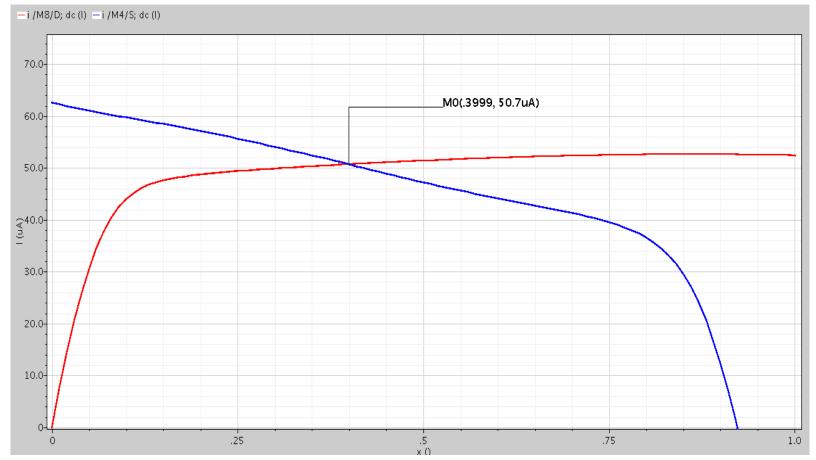

→ Step size of the control voltage = 0.2896 mv As  $\Delta v = \frac{\Delta t * I}{C} = \frac{85.851psec*50.6uA}{15pF} = 0.2869mv$ → This is equivalent to 0.17 degree → So the PI resolution become 531 point per quad → Power consumption = 1.4m

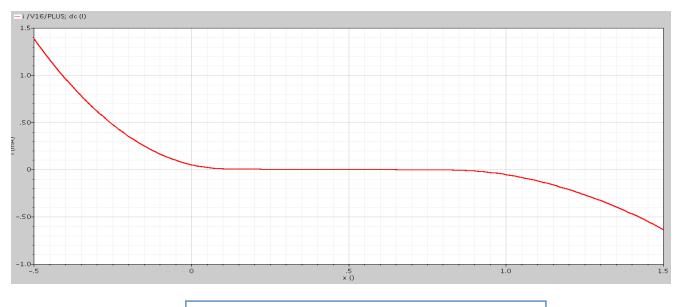

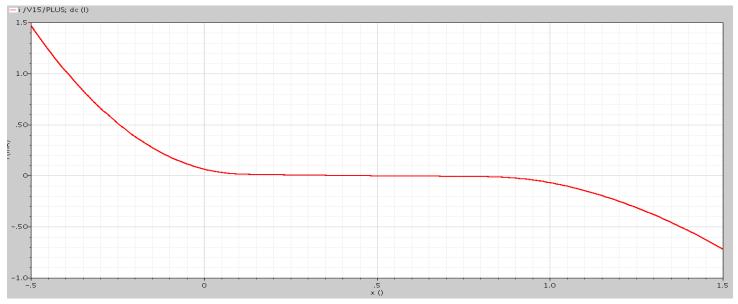

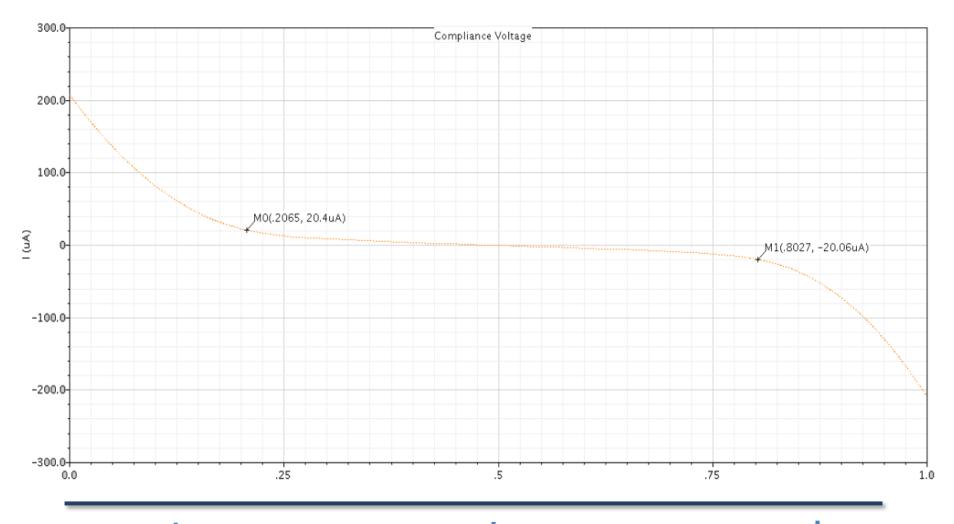

#### **Compliance Range:**

1-The compliance range of the charge pump itself without the biasing were from 118.5mv to 791.2 mv

Compliance range of the CP itself

### Simulation Results (cont.)

2-After adding the bias current sources as they are cascaded the range decreased to from 271.1mv to 573m

$\rightarrow$  As the PI works from 300 mv to 500 mv , the range was accepted.

**Compliance range of the CP with bias current sources**

### **Simulation Results (cont.)**

#### **Simulation of PD + CP**

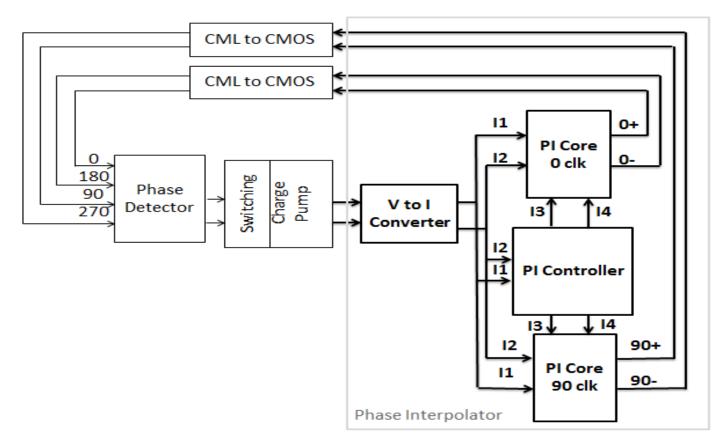

### Analog Phase Interpolator (PI)

Presented by : Samar Magdy

#### **Outlines**

- Introduction to Analog PI.

- PI in System Architecture.

- Concept and Circuit Review.

- Final Results.

- CDR Loop Locking.

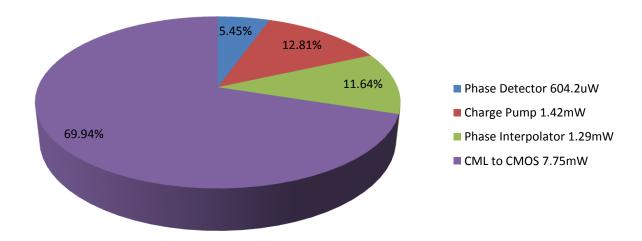

- **CDR Power Consumption.**

#### **Introduction to Analog PI**

- Digital PI Drawbacks.

- Degrades CDR Jitter Performance.

- > Speed Limitations.

- Power Dissipation.

- Analog Phase Controller Advantage.

#### **PI in System Architecture**

7/10/2013

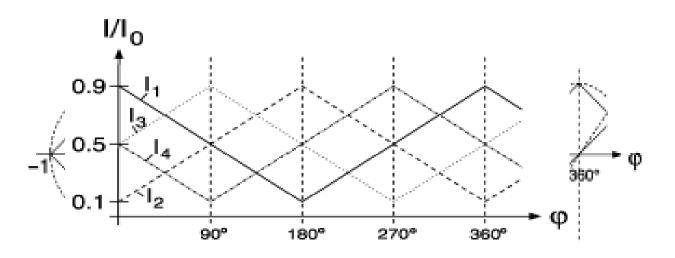

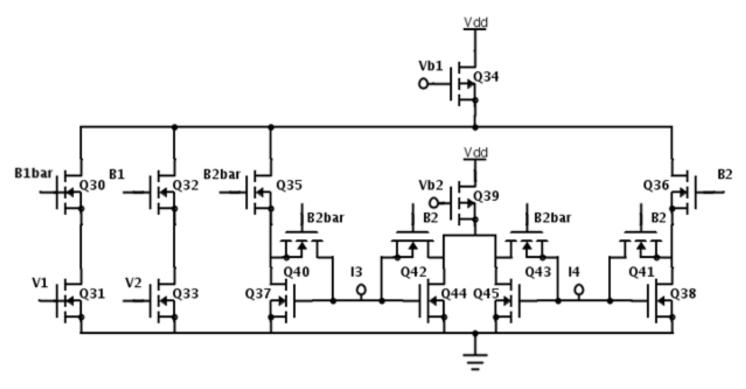

## **Concept & Circuits Review**

- Interpolation Concept.

- Currents Generation Concept.

- Clocks 0° and 90° PI Cores.

- V-to-I Converter.

- PI Controller.

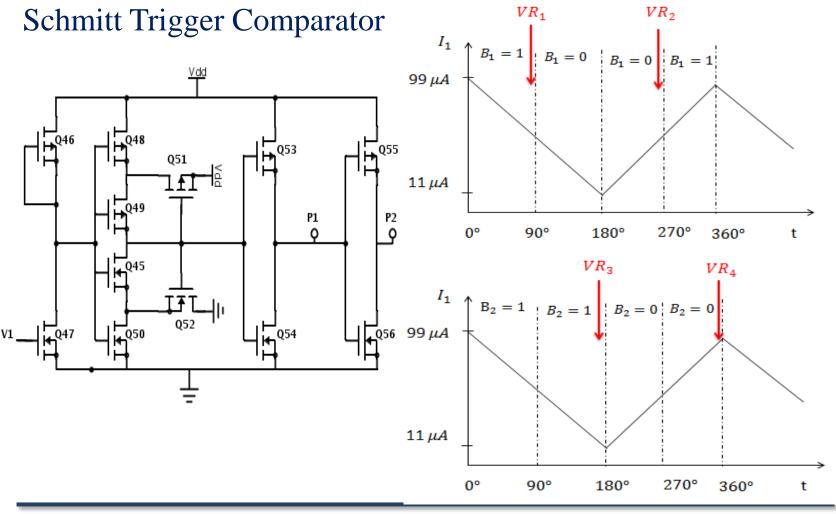

- Schmitt Trigger Comparators.

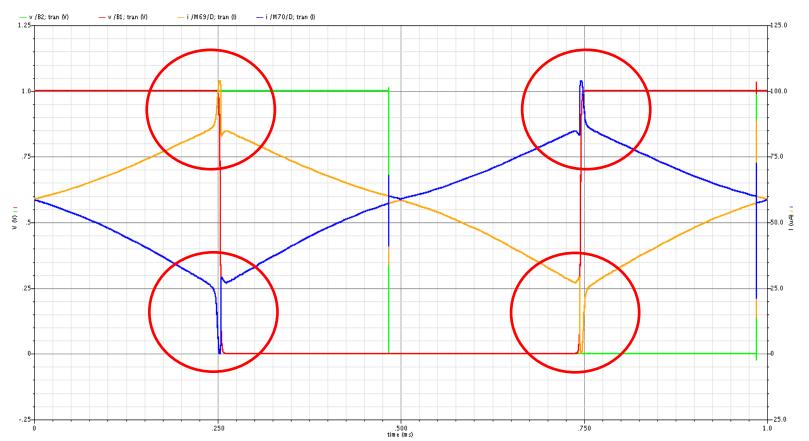

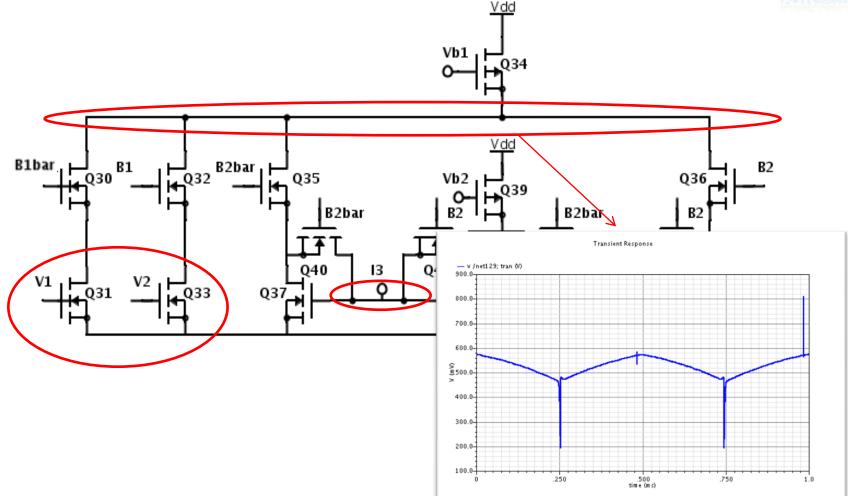

- Spikes Suppression and Voltage Clamping

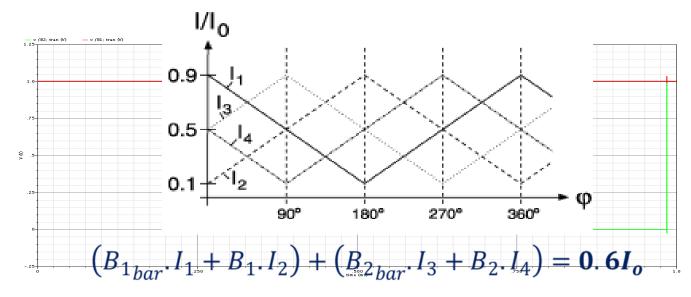

#### Interpolation Concept

#### Sweeping $\Delta Vin$ for the same vdd = 1v with diff $V_{cm}$

- $a_1^2 + a_2^2 = constant$  "circle Raduis"

- Linear Approximation  $\mathbf{a_1} + \mathbf{a_2} = constant$

A 10 GB/s CMOS Clock and Data Recovery with an Analog Phase Interpolator.(Langman,Rainer,Zimmermann,Takuma,H.Siedhoff

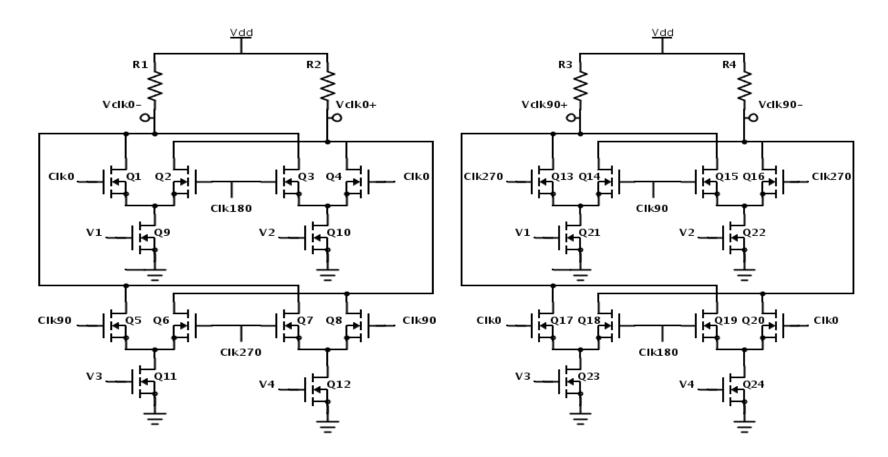

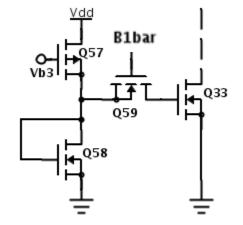

#### Clocks 0° and 90° PI Cores

7/10/2013

A 10 GB/s CMOS Clock and Data Recovery with an Analog Phase Interpolator.(Langman,Rainer,Zimmermann,Takuma,H.Siedhoff

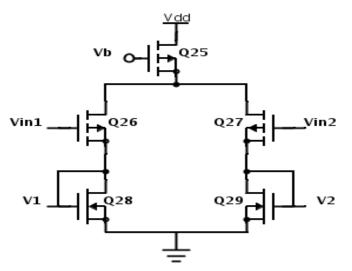

#### V-to-I Converter

| Input Ports   | Max-DC value | Min-DC value |

|---------------|--------------|--------------|

| Vin1 and Vin2 | 500mV        | 300mV        |

| Output Ports | Max-DC value | Min-DC value |

|--------------|--------------|--------------|

| V1 and V2    | 690.5mV      | 420.5mV      |

Transient Response

A 10 GB/s CMOS Clock and Data Recovery with an Analog Phase Interpolator.(Langman,Rainer,Zimmermann,Takuma,H.Siedhoff

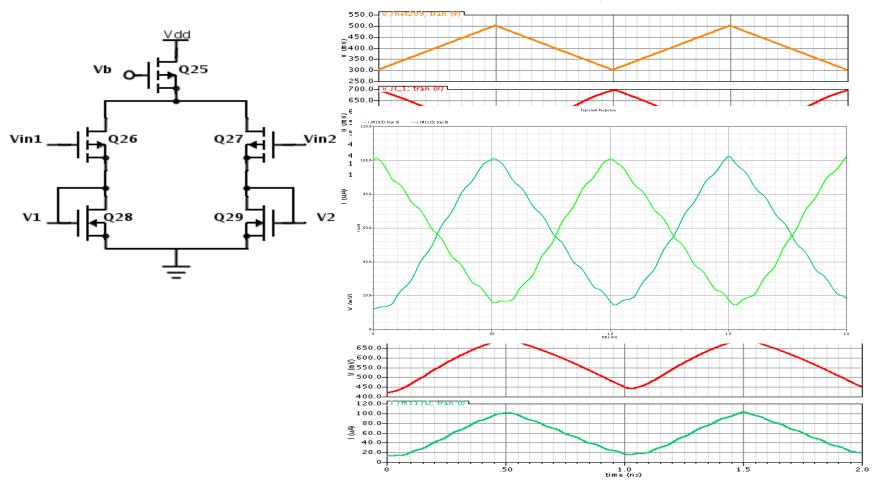

| Quads           | $B_1 B_2$ |

|-----------------|-----------|

| 1 <sup>st</sup> | 11        |

| 2 <sup>nd</sup> | 01        |

| 3 <sup>rd</sup> | 00        |

| 4 <sup>th</sup> | 10        |

PI Controller

7/10/2013

A 10 GB/s CMOS Clock and Data Recovery with an Analog Phase Interpolator.(Langman, Rainer, Zimmermann, Takuma, H.Siedhoff

Transient Response

#### 7/10/2013

A 10 GB/s CMOS Clock and Data Recovery with an Analog Phase Interpolator.(Langman,Rainer,Zimmermann,Takuma,H.Siedhoff

7/10/2013

A 10 GB/s CMOS Clock and Data Recovery with an Analog Phase Interpolator.(Langman,Rainer,Zimmermann,Takuma,H.Siedhoff

ASU-MIPEX Graduation Project 2013

190

#### Spikes Suppression and Voltage Clamping

#### Spikes Suppression and Voltage Clamping

7/10/2013

A 10 GB/s CMOS Clock and Data Recovery with an Analog Phase Interpolator.(Langman,Rainer,Zimmermann,Takuma,H.Siedhoff

### **Final Results**

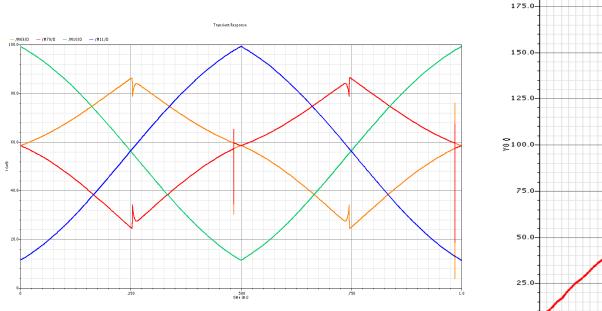

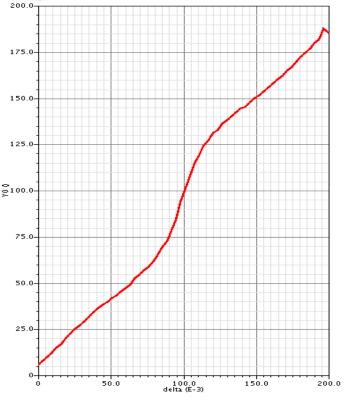

— Trial

$K_{PI} = 0.5851^{\circ}mV$

A 10 GB/s CMOS Clock and Data Recovery with an Analog Phase Interpolator.(Langman, Rainer, Zimmermann, Takuma, H.Siedhoff

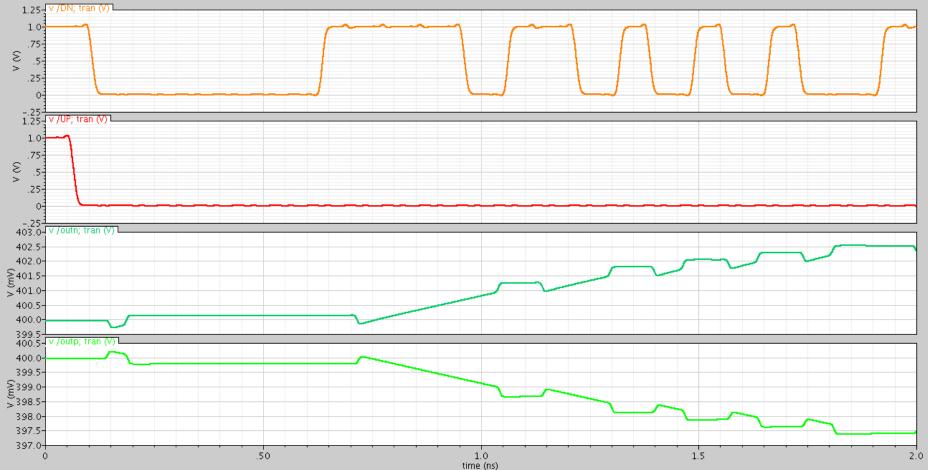

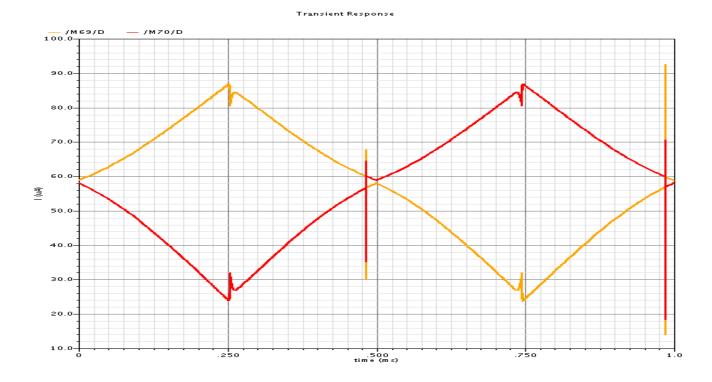

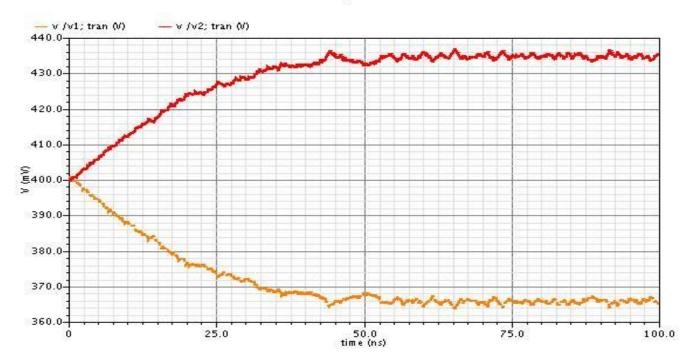

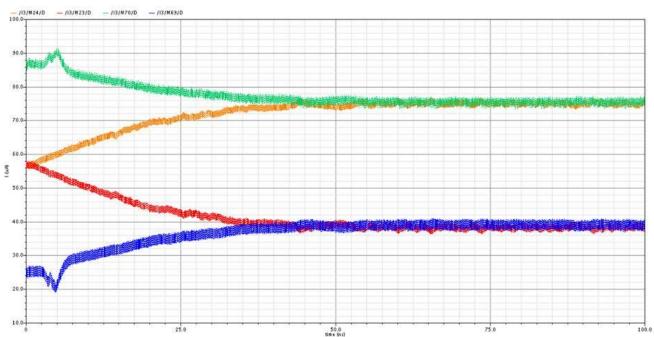

## **CDR Loop Locking**

Transient Response

A 10 GB/s CMOS Clock and Data Recovery with an Analog Phase Interpolator.(Langman, Rainer, Zimmermann, Takuma, H.Siedhoff

## **CDR Loop Locking**

Transient Response

A 10 GB/s CMOS Clock and Data Recovery with an Analog Phase Interpolator.(Langman, Rainer, Zimmermann, Takuma, H.Siedhoff

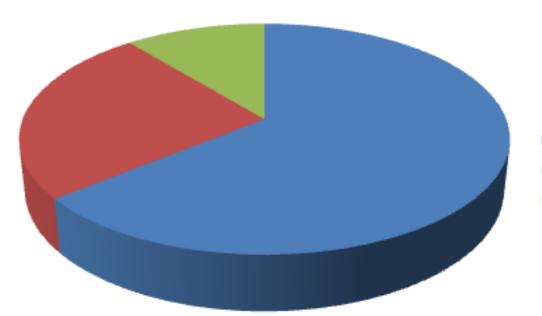

## **CDR Power Consumption**

#### Total Power Consumption 11.08 mw

7/10/2013

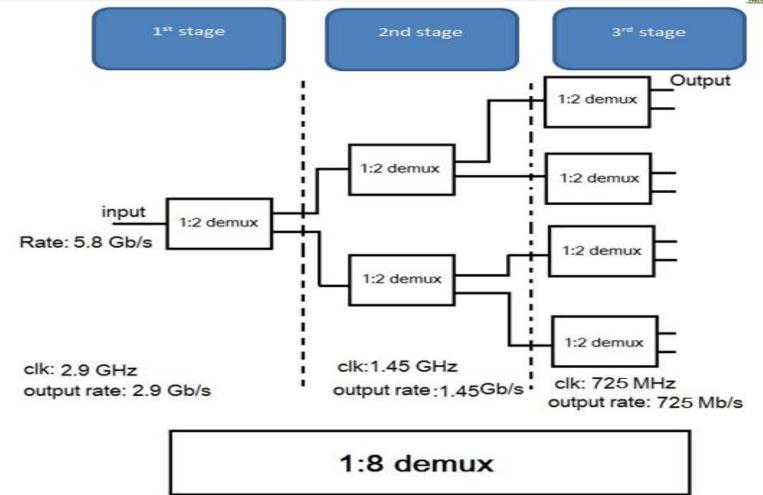

# De-Serializer (De-MUX)

Presented by : Ahmed Hesham

## Outlines

- Introduction

- Basic concepts

- Architecture

- Topologies

- Simulation and Results

- References

- Questions

## Introduction

- **De multiplexing:** Transferring serial input data into parallel output. that allows lower frequency relative to data rate.

- The Demux circuit is the far end of our system.

- The input is a 2 single ended lines from the phase Interpolator with data rate equals 5.8 Gb/s.

- The output is 16 single ended lines with data rate 725 Mb/s.

## **Basic Concepts**

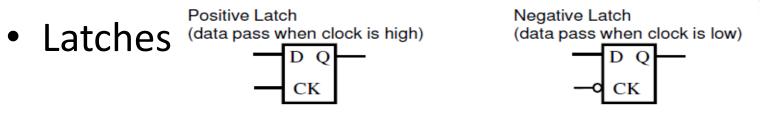

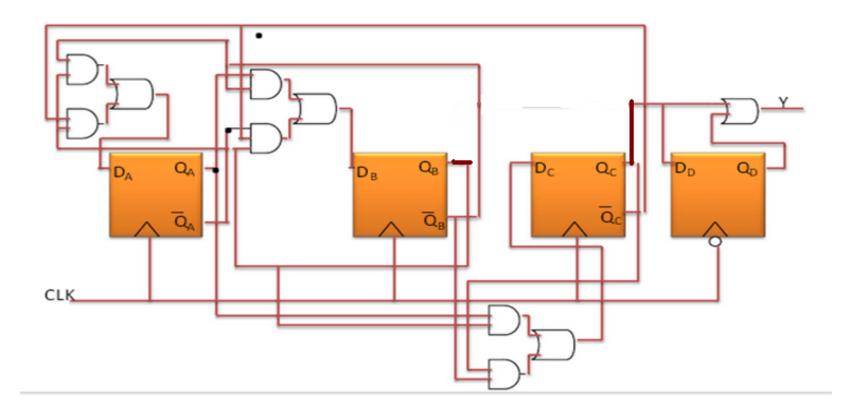

- Master-Slave Flip Flops: Two latches can be connected as Master& salve to operate as a flip flop.

- Clocked Inverters:

- is an inverter that controls its output by a clock.

- If clk = 1, Inverter pass the input to output & If clk = 0, it holds the data as a latch (high impedance).

## Architecture

#### 203

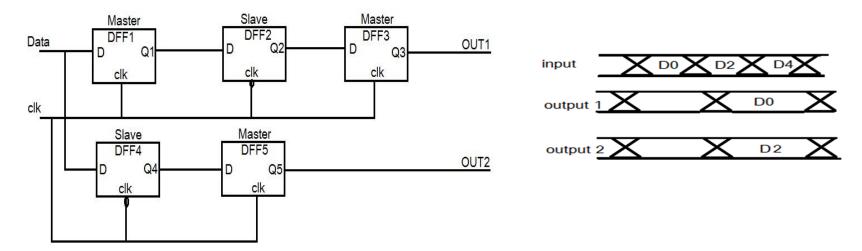

• The conventional 1:2 Demux cell using 5 Latches

- DFF1, DFF2 makes a falling edge master-slave trigger

- DFF4, DFF5 makes a raising edge master-slave trigger

- In order to synchronize both outputs (1&2) DFF3 is used (half a duty cycle delay)

#### 204

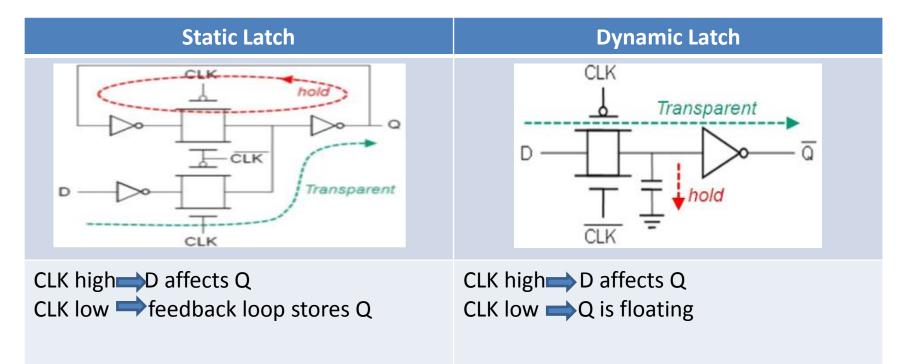

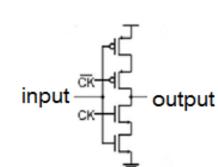

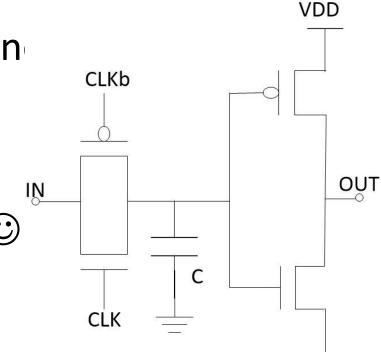

## CMOS Dynamic Latch

- CLK high > IN affects Out n

- CLK low —Out Floating

- Advantage:

Topologies

- Low power consumption <sup>(C)</sup>

- Can Handle high speed 😳

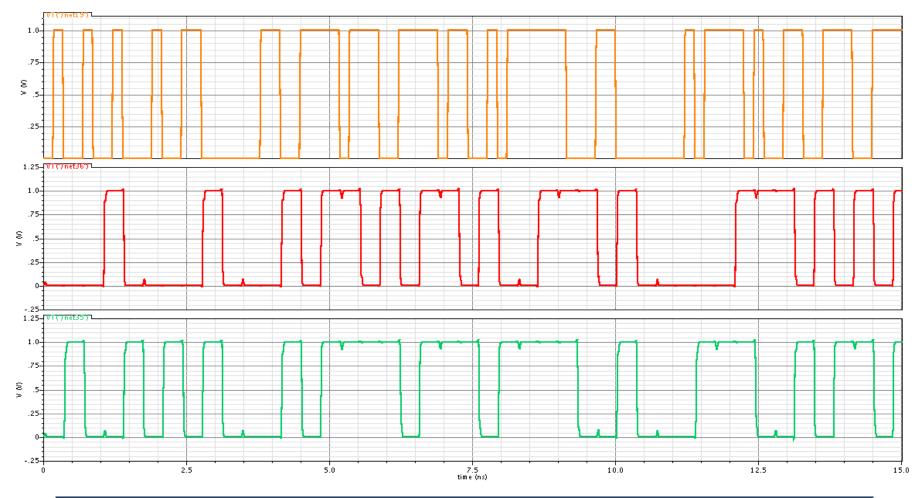

## Simulation & Results(1)

## Simulation & Results(2)

#### Transient Response

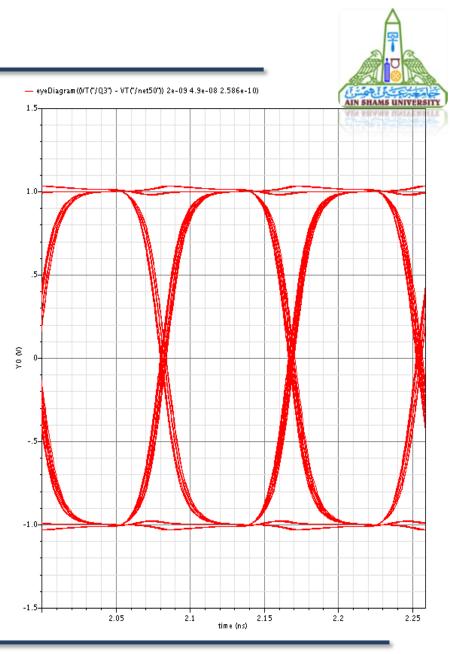

## **Simulation & Results**

#### - eyeDiagram DTC/out25 0 1e-07 2.76e-030

## References

- 1-Kehrer D, Wohlmuth H D, Knapp H, et al. 40-Gb/s 2:1 multi-plexer and 1:2 demultiplexer in 120-nm standard CMOS. IEEEJ Solid-State Circuits, 2003, 38(11): 1830

- [2] Kanada K, Yamazaki D, Yamamoto T, et al. 40 Gb/s 4:1MUX/1:4 DEMUX in 90 nm standard CMOS. IEEE Int Solid-State Circuits Conf Tech Dig, 2005: 152055007-4

- Zhang Changchun et al. May 2009

- [3] Kim B G, Kim L S, Byun S, et al. A 20 Gb/s 1:4 DEMUX with-out Inductors in 0.13\_m CMOS. IEEE Int Solid-State CircuitsConf Tech Dig, 2006: 528

- [4] Chien J C, Lu L H. A 20-Gb/s 1:2 demultiplexer withcapacitive-splitting current-mode-logic latches. IEEE TransMicrow Theory Tech, 2007, 55(8): 1624

- [5] Rein H M, Moller M. Design considerations for very-high-speed Si bipolar IC's operating up to 50 Gb/s. IEEE J Solid-State Circuits, 1996, 31(8): 1076

- [6] 0165.Digital Integrated Circuits (2nd Edition) by Jan M. Rabaey

#### **Receiver power consumption**

CDR (11.04mw)

CTLE (2.4mw)

DeMUX (.449mw)

# Phase Locked Loop (PLL)

# PFD/CP/LF

Presented by : Eman Salah El-Din

### Outlines

- PFD/CP/LF Block Diagram

- Circuit Design

PFD

Charge Pump/LF

Simulation Results

PFD

Charge Pump/LF

Corners

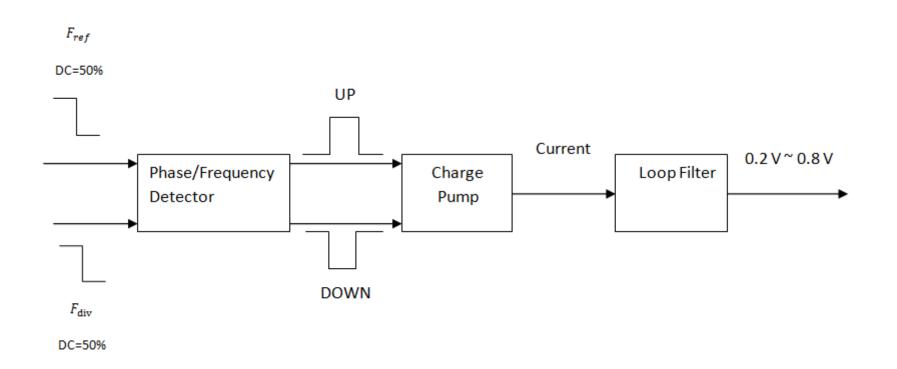

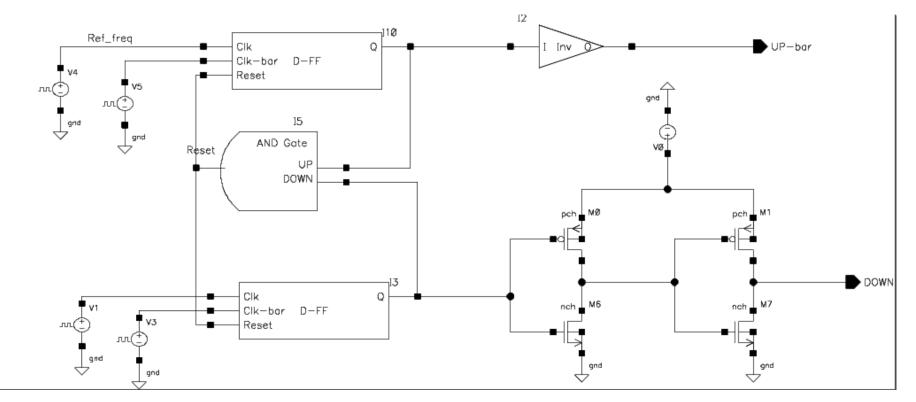

## PFD/CP/LF: Block Diagram

## **PFD Circuit**

## **CP Circuit**

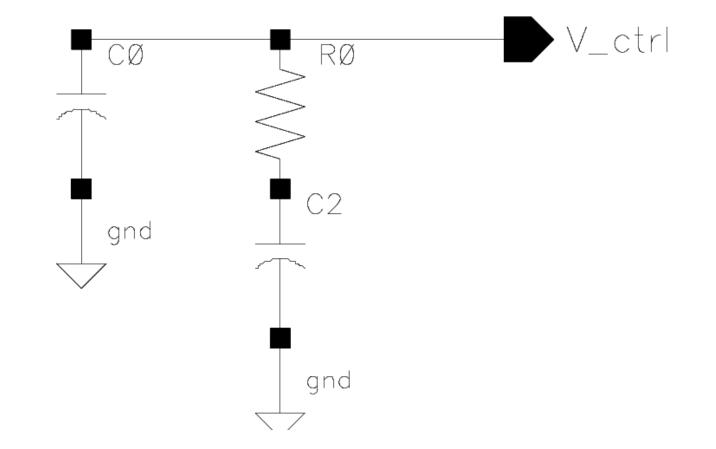

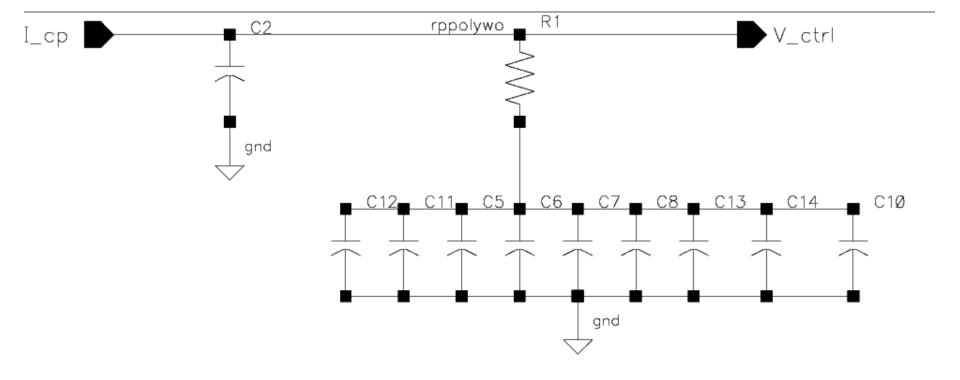

## **Loop Filter**

### **Loop Filter**

Transient Response

### CP: Results: Matching

7/10/2013

### **CP: Results:** Compliance Voltage

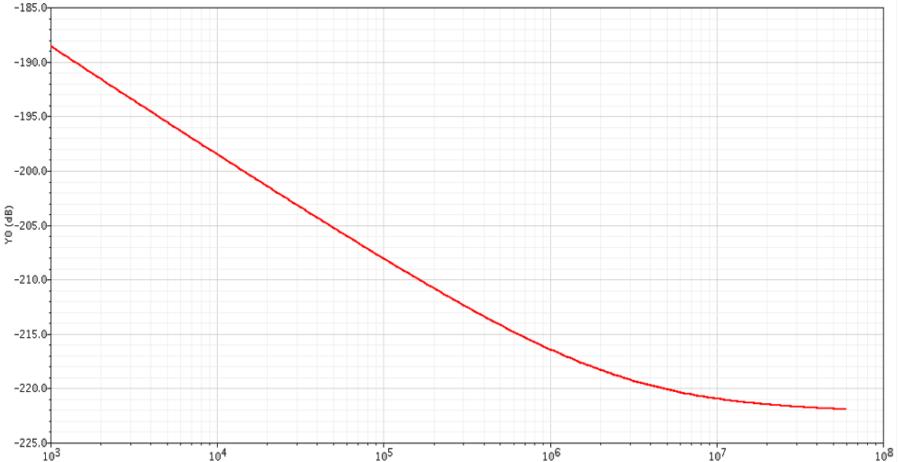

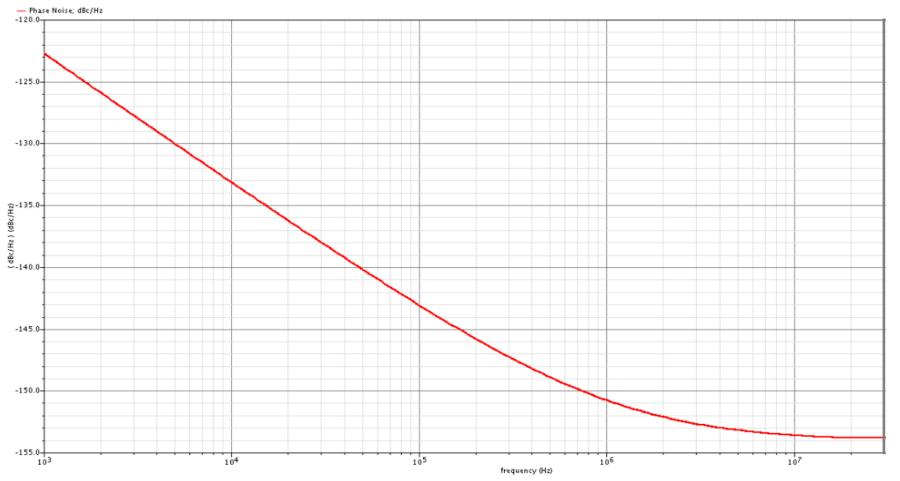

### PFD/CP: O/P Current Noise

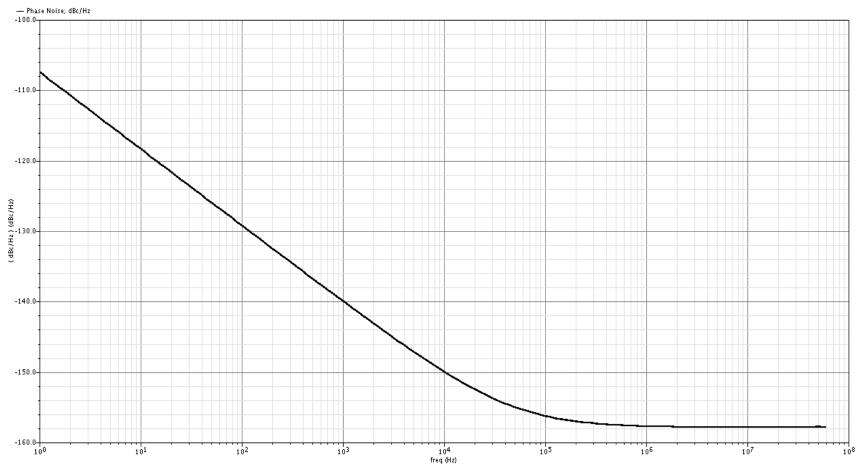

### PFD/CP: Phase Noise

Transient Response

### **Power Consumption**

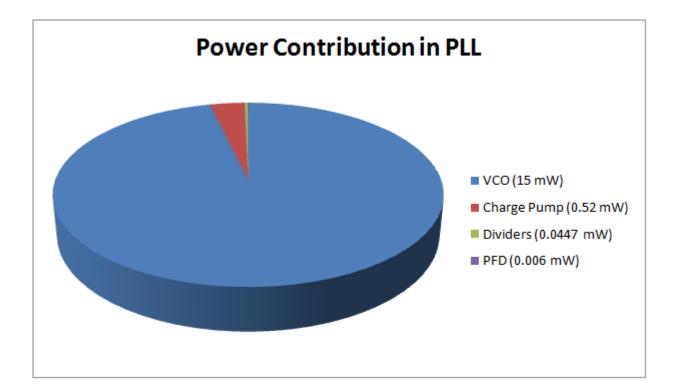

• Power consumption of PFD=6  $\mu$ W. •Power consumption of CP=0.52 mW.

### **Corners:**

Using Ocean Code, it was found that:

- The PFD is robust across PVT.

- •The CP is robust across PVT.

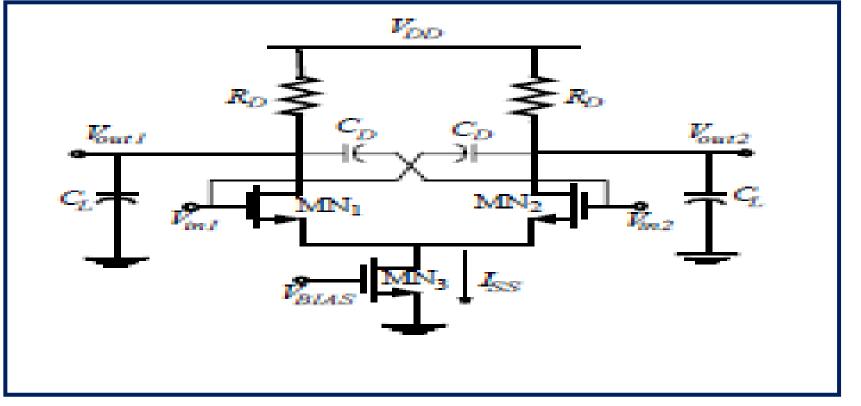

# Voltage Controlled Oscillator (VCO)

Presented by : Alaa El-Din M. Hamed

### **VCO Outlines**

- Ring VCO vs LC VCO

- Maneatis delay cell

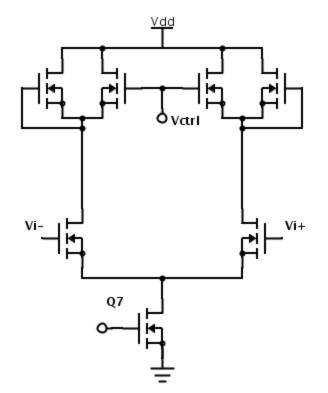

- Differential amplifier with variable negative resistance

- DCVSL

- DCVSL-R

- DCVSL-R VCO

- DCVSL-R VCO Final

- Final Results

## **Ring VCO vs LC VCO**

| РОС                       | Ring Oscillator                    | LC Oscillator           |

|---------------------------|------------------------------------|-------------------------|

| Operation                 | Astable                            | uses LC Resonator       |

| Output Waveform           | non-sinusoidal<br>(usually square) | Sinusoidal              |

| Output Phase noise        | High                               | Low                     |

| Output Spectral<br>purity | High harmonic content              | Low harmonic<br>content |

| Area on chip              | Small                              | Large                   |

| Power consumption         | High                               | Low                     |

## **Ring VCO vs LC VCO**

As This PLL is used a clock generator for a serial links

interface, small area is the main criterion. So, a ring VCO

was chosen.

Now, Let's ahead to the three topologies which I

designed, problems faced and the final design.

### Maneatis delay cell

### Maneatis delay cell

This is called a symmetric load as

it it has two equally sized

transistors to linearize the tuning sensitivity as follows:

$$R_{eff} \approx \frac{1}{g_m} = \frac{1}{\beta (V_{ctrl} - V_T)} = \frac{1}{\sqrt{2 \beta I_D}}$$

$$t_d \approx R_{eff} C_{eff} = \frac{C_{eff}}{\beta (V_{ctrl} - V_T)}$$

$$f_{osc} = \frac{1}{2 N t_d} = \frac{\beta}{2 N C_{eff}} \cdot (V_{ctrl} - V_T)$$

7/7/2013J. Maneatis, "Low-Jitter Process-Independent DLL and<br/>PLL Based on Self-Biased Techniques," *IEEE J. Solid-*<br/>*State Circuits*, Vol. 31, no. 11, pp.1723-1732, Nov 1996.

ASU-MIPEX Graduation Project 2013

### Maneatis delay cell

Problems that I faced during designing this

topology:

- 1. Low supply voltage.

- 2. Short Channel effects (mainly small output

resistance) limited the gain requiring large

number of delay cells consuming extra power

and limiting the speed considerably.

### So, I headed for the next topology.

7/7/2013

J. Maneatis, "Low-Jitter Process-Independent DLL and PLL Based on Self-Biased Techniques," *IEEE J. Solid-State Circuits*, Vol. 31, no. 11, pp.1723-1732, Nov 1996.

### Diff. amp. with negative res.

7/7/2013

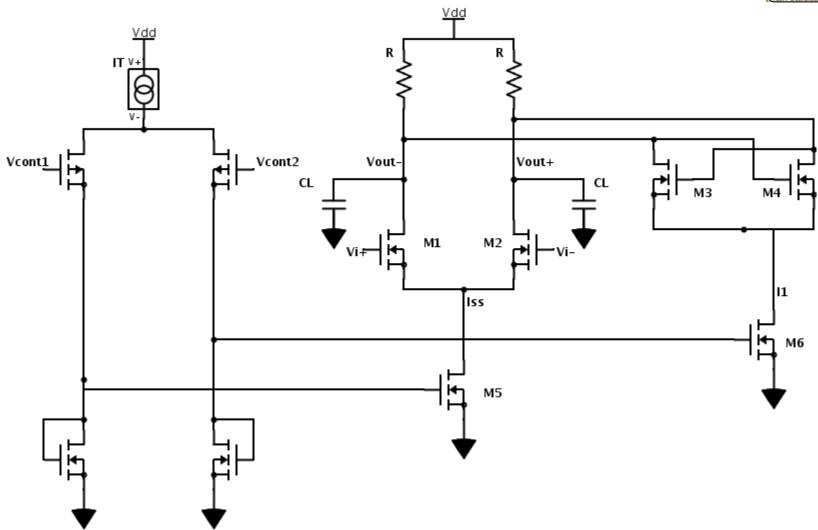

## Diff. amp. with negative res.

$$t_d \approx R_{eff} C_{eff}; R_{eff} = R - \frac{1}{g_{m,neg}}$$

$$g_{m,neg} = \sqrt{2\beta I_1}; I_1 = \beta_{cont2} (V_{cont2} - V_T)^2$$

$$g_{m,neg} = \sqrt{2\beta\beta}_{cont2} (V_{cont2} - V_T)$$

$$f_{osc} = \frac{1}{2 N t_d} = \frac{\beta}{2 N C_{eff}} \cdot \frac{1}{R - \sqrt{2 \beta \beta_{cont2}} (V_{cont2} - V_T)}$$

7/7/2013

B. Razavi, " Oscillators," Design of CMOS Analog Integrated Circuits

ASU-MIPEX Graduation Project 2013

## Diff. amp. with negative res.

Problem faced me during designing this topology, R was small (due to high frequency) requiring high  $g_{m,neg}$  and  $g_{m,i/p}$  (to be able to tune VCO for required frequency range) so when increasing  $I_1$  and  $I_{ss}$ , IR drop increased leading to less  $V_{od}$  for cross coupled MOSFETs entering subthreshold region.

### DCVSL

Vi+

Pseudo nMOS inverter

7/7/2013

DCVSL (**D**ifferential **C**ommon **V**oltage **S**witch **L**ogic)

Vi-

Vdd

A. Mason. ECE 410. Class Lecture, Topic:"Advanced Digital", College of Engineering, Michigan State University, Spring, 2008

Advantages:

Rail-to-rail swing.

Nearly no static power consumption

#### **Disadvantages:**

Asymmetric transitions.

Solution:

Decrease  $t_{PLH}$ .

## 7/7/2013D. Turker, S. Khater, E. Sinencio, " A DCVSL Delay Cell<br/>for Fast Low Power Frequency Synthesis Application,"<br/>*IEEE Transactions on Circuits and Systems I: Regular*<br/>*Papers*, Vol. 58, no. 6, pp.1225-1238, Jun. 2011.

ASU-MIPEX Graduation Project 2013

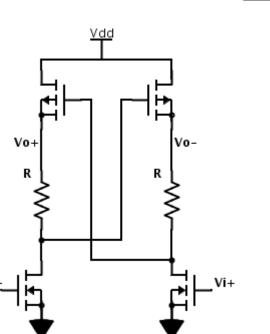

## DCVSL-R

Introduce extra IR drop such that the voltage of gates of pMOS decrease faster leading to less t<sub>PLH</sub>. Also, this will not affect t<sub>PHL</sub> as long as R < R<sub>nMOS,on</sub>. So, R is designed for symmetric

transitions.

### **DCVSL-R VCO**

tuning is limited by the  $V_{CM}$  of output (nearly 500 mV) making  $K_{VCO}$  too high which is undesirable.

D. Turker, S. Khater, E. Sinencio, "A DCVSL Delay Cell for Fast Low Power Frequency Synthesis Application," *IEEE Transactions on Circuits and Systems I: Regular Papers*, Vol. 58, no. 6, pp.1225-1238, Jun. 2011.

ASU-MIPEX Graduation Project 2013

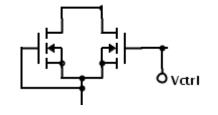

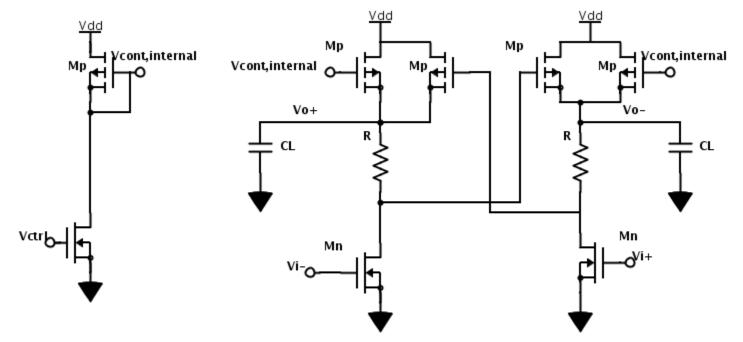

### **DCSL-R VCO Final**

Here is the solution.

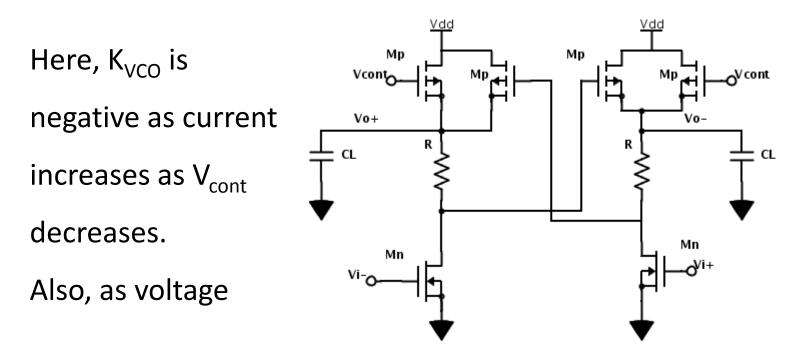

$K_{VCO}$  is now positive as required in addition to that the tuning voltage range now increases which leads to less  $K_{VCO}$ .

D. Turker, S. Khater, E. Sinencio, "A DCVSL Delay Cell for Fast Low Power Frequency Synthesis Application," *IEEE Transactions on Circuits and Systems I: Regular Papers*, Vol. 58, no. 6, pp.1225-1238, Jun. 2011.

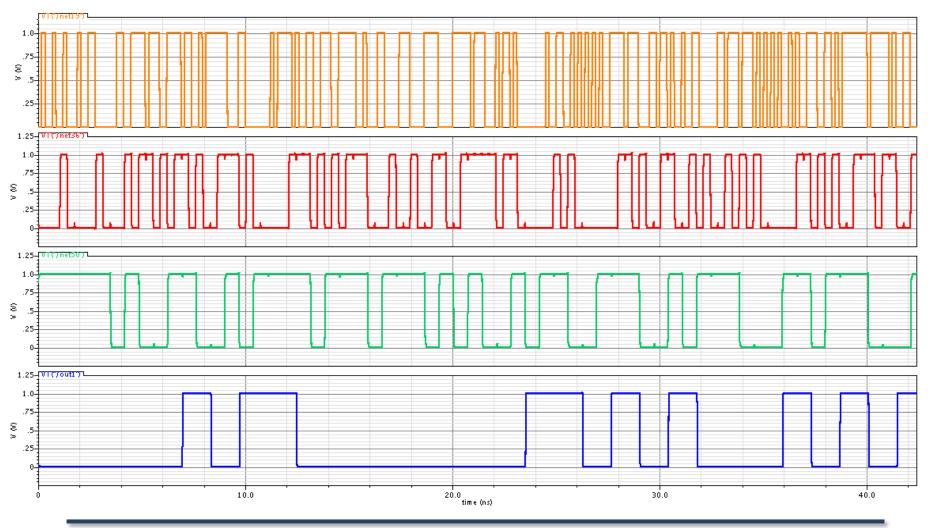

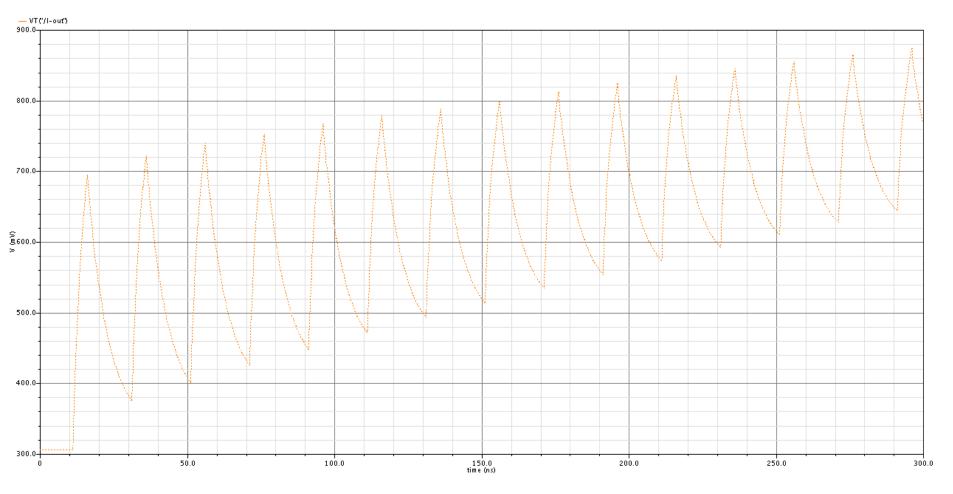

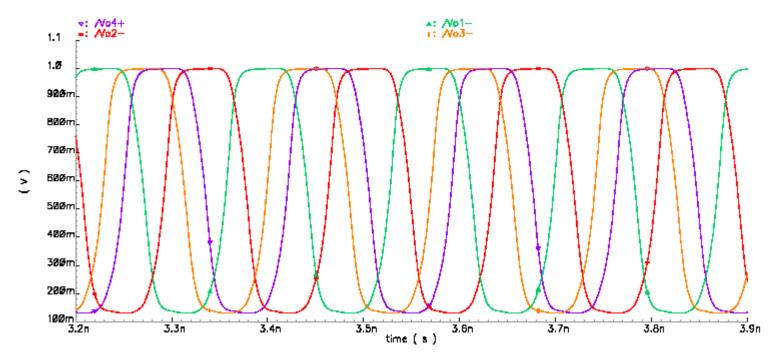

Output Waveforms (Vo1- and Vo3- are in quadrature)

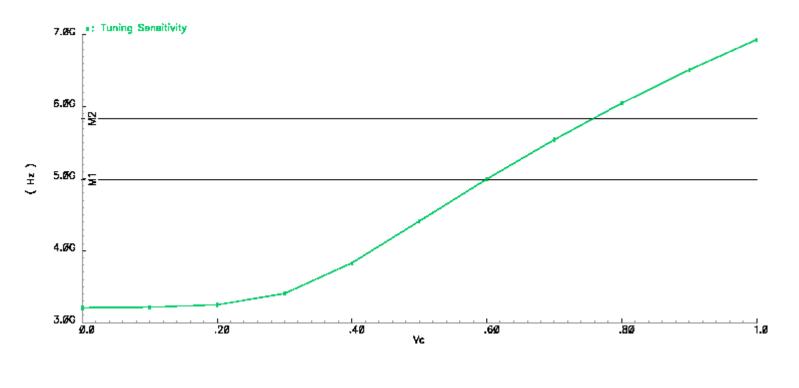

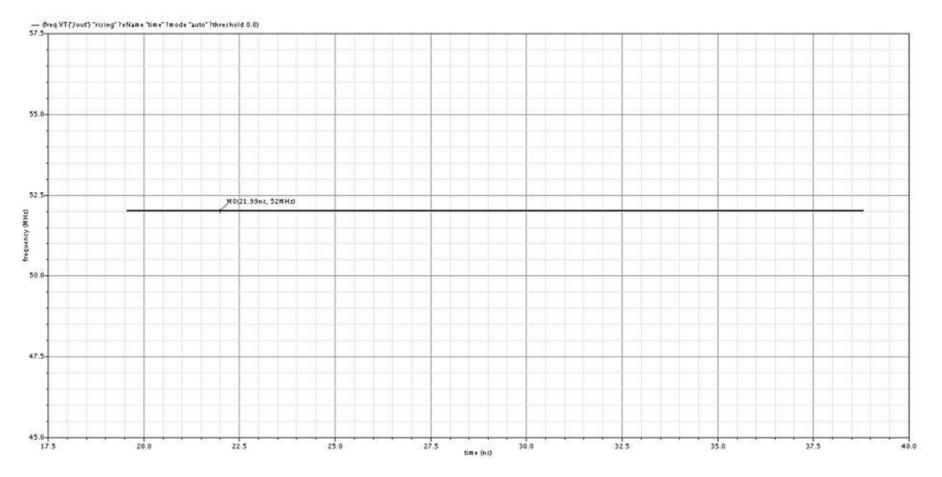

$K_{VCO} = 5.3193 \text{ GHz/V}.$

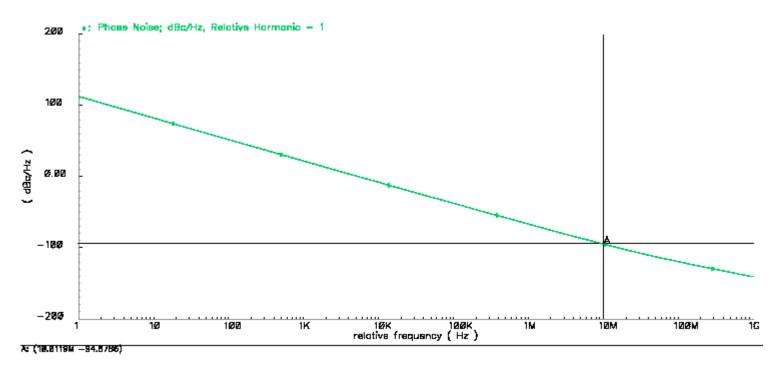

#### Phase noise = -95 dBc/Hz at 10 MHz offset

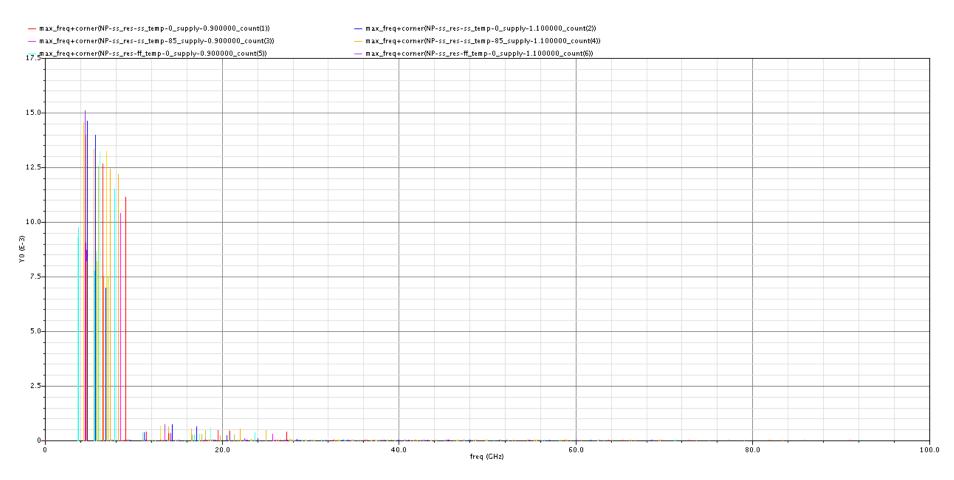

#### Phase noise across corners

7/7/2013

Output Power across corners (worst case is 15 mW)

7/7/2013

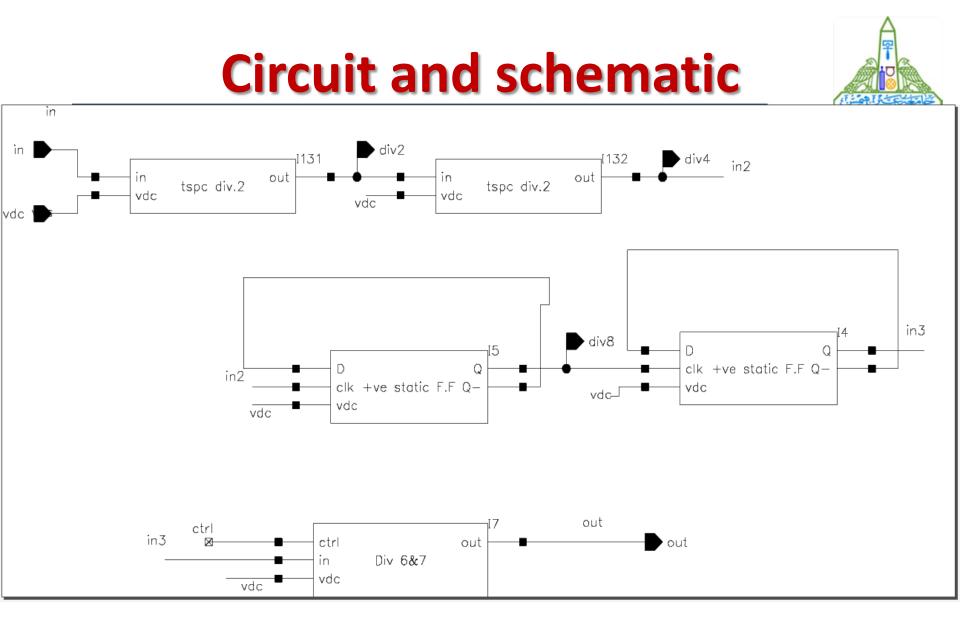

## Dividers

Presented by : Basma Atef

### Outlines

- Block diagram

- Circuit

- -TSPC

- -Static flip flop

- -Divide by 6&7

- -Divide by 7

- -Divide by 6

- Simulations & Results

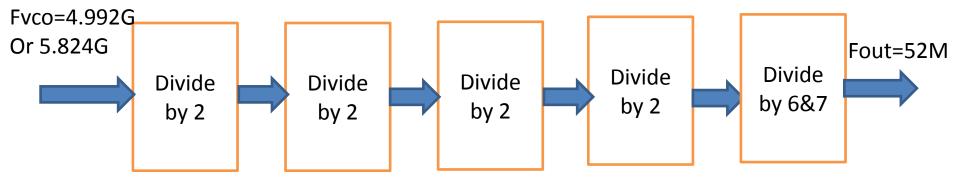

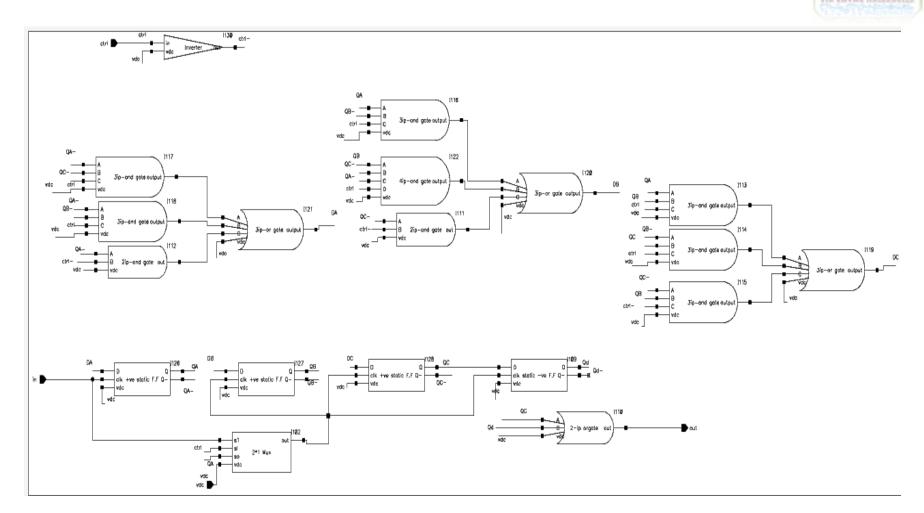

### **Block Diagram**

Division ratio =96 or 112

### **TSPC circuit**

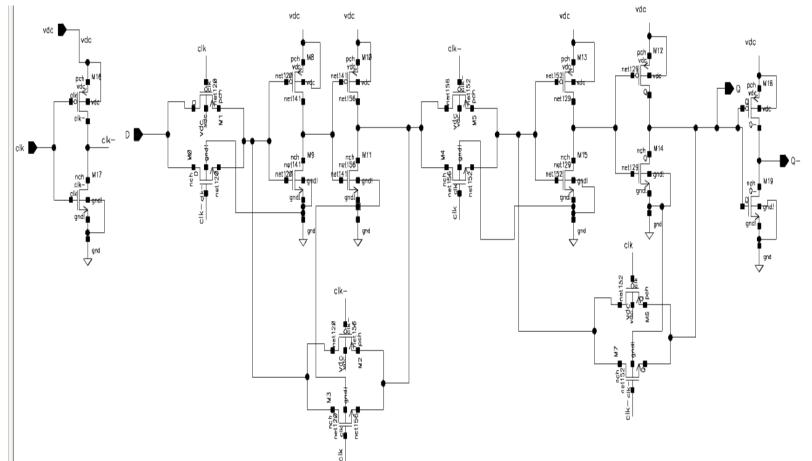

### **Static flip flop circuit**

# **Divide by 7 circuit**

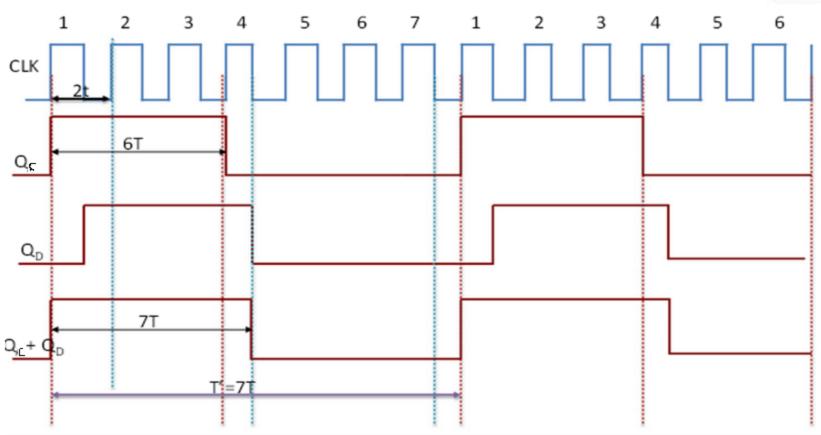

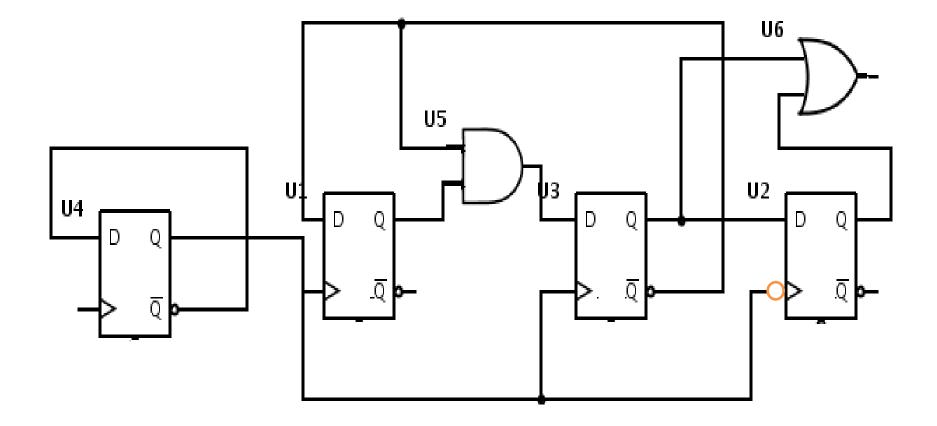

#### Divide by 7 counter Logic Diagram

# **Divide by 7 circuit**

#### **Divide by 6 circuit**

Transient Response

Periodic Noise Response

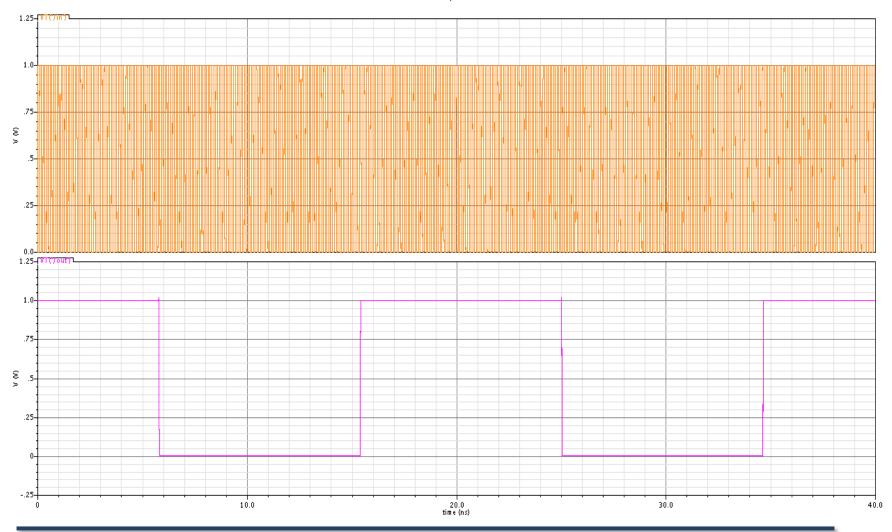

# **Simulations & results**

- Power consumption = 44.7uw.

- Circuit is robust across corners.

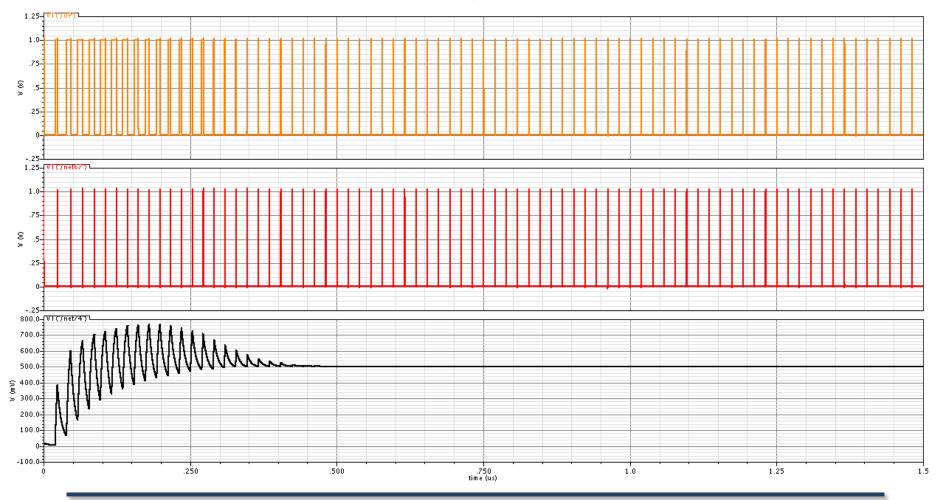

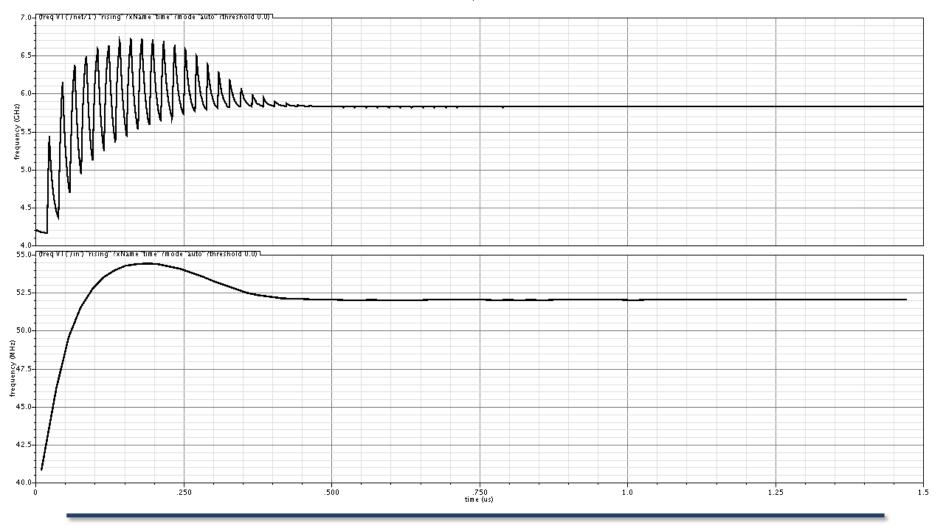

# **The Locked Loop**

Transient Response

7/10/2013

#### Transient Response

7/10/2013

# **The Locked Loop**

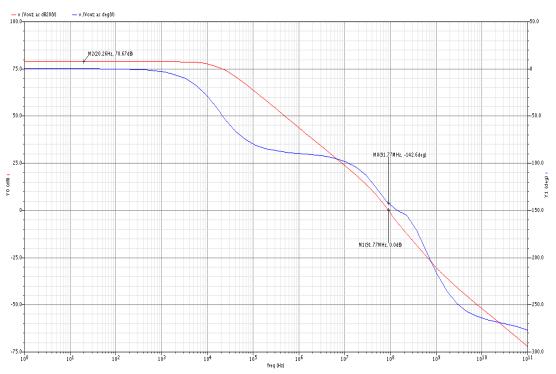

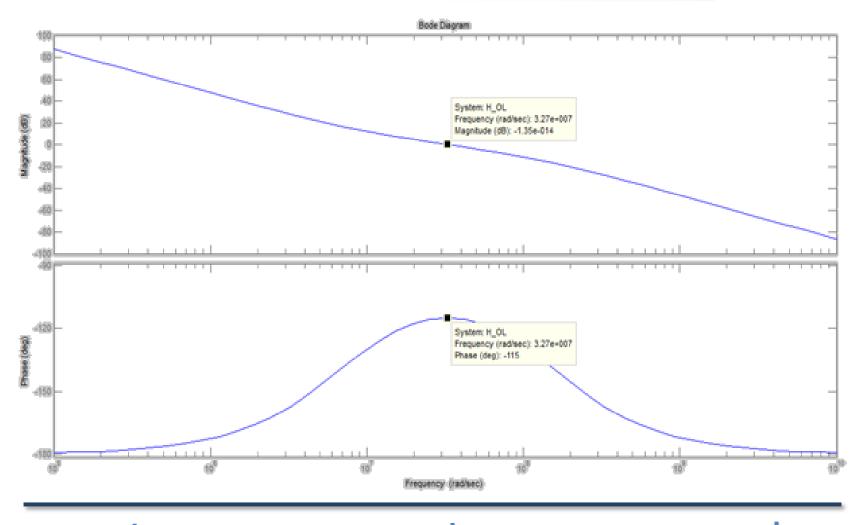

# The Locked Loop: Open Loop

7/10/2013